ニュース

A-Dコンバータを用いた新方式PLLを開発:新技術(2/2 ページ)

東京工業大学は2015年3月10日、同大学教授の松澤昭氏らの研究グループが、A-Dコンバータを用いた新しい方式のデジタルクロック生成器の開発に成功したと発表した。

65nm CMOSプロセスを用いて試作

こうした利点により、電圧差による位相検出の方が、より高分解能かつ低消費電力な特性を実現できるとする。同大学では、「デジタルPLLにこのADCによる位相検出器を用いれば、非常に低い帯域内位相雑音かつ低ジッタ特性の実現が可能となる。消費電力も低くできる」としている。

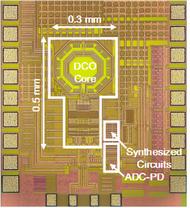

同研究グループは、A-Dコンバータを用いた新規デジタルPLLを、65nm シリコンCMOSプロセスで試作し、4.2mWの消費電力を用い、2.2GHzの周波数で発振させることに成功。帯域内位相雑音は−112dBc/Hz、クロックの揺れを表すジッタ特性は、RMS値で380fs、発振周期に対して0.08%という値を達成したとする。

| 新方式ADC型PLL | C. Hsu JSSC'09 | C.Yao JSSC'13 | Chilara ISSCC'14 | |

|---|---|---|---|---|

| 方式 | ADC-based | TDC-based | TDC-based | TDC-based |

| 周波数 | 2.2GHz | 3.6GHz | 2.7GHz | 2.4GHz |

| RMSジッタ | 380fs | 200fs | 230fs | 1.71ps |

| 帯域内 位相雑音 |

−112dBc/Hz | −107dBc/Hz | −110dBc/Hz | −90dBc/Hz |

| PLL FoM | −242dB | −237dB | −240dB | −236dB |

| 消費電力 | 4.2mW | 47mW | 17mW | 0.9mW |

| 面積 | 0.15mm2 | 0.95mm2 | 0.62mm2 | 0.20mm2 |

| 東京工業大学の発表資料より作成 | ||||

同大学は、「無線機の小型・低消費電力化、マイクロプロセッサや専用LSIの大幅な低消費電力化・高速化・小型低価格化に威力を発揮する技術といえる。超小型バッテリーレスセンサーなどあらゆる機器に組み込むことが期待される」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

RF(高周波)編:次世代ウェアラブルを支える最先端の無線回路技術

RF(高周波)編:次世代ウェアラブルを支える最先端の無線回路技術

ISSCC2015では、RF関連の発表件数が27件と、かなり多い。これらは3つのセッションに分かれて発表される。今回は、3つのセッションに沿って、RF関連の注目論文を紹介していこう。 サイプレス、5年ぶりのタイミング製品を投入

サイプレス、5年ぶりのタイミング製品を投入

Cypress Semiconductor(以下、サイプレス)は2015年4〜6月に、プログラマブルクロックジェネレータ「CY27410」を量産出荷すると発表した。同社がクロック関連製品を投入するのは、約5年ぶり。 第11回 高周波出力に対応した水晶発振器を解説

第11回 高周波出力に対応した水晶発振器を解説

今回は、特定の用途に向けて仕様を最適化した水晶タイミングデバイスのうち、通信機器やネットワーク機器を対象にした品種を紹介します。 位相雑音測定器が多彩に、最適機は用途で選ぶ

位相雑音測定器が多彩に、最適機は用途で選ぶ

位相雑音を高い精度で手軽に測定できることを売りにした測定器が、最近になって相次いで登場している。それらは、それぞれ特徴的な機能を備えるほか、利害得失がある。従って、「最適」な測定器は測定対象とする信号源や、測定結果をどのように活用したいかによって違う。各測定器の特徴や使いどころを解説する。- シリコンタイミング 〜 水晶市場を狙う新提案が続々

半世紀ほど前に、電子部品の世界で大きな世代交代が起きた。かつて主役を担った真空管に取って代わって、Si(シリコン)技術で製造するトランジスタがその座に着いたのである。「発振器にも、同じ変革が起きる」――。これまで発振器の市場では、水晶発振器が絶対的な地位を築いてきた。今その交代劇をもくろむのは、シリコン技術で製造するMEMS発振器やCMOS発振器を手掛ける半導体ベンダーだ。シリコン化の最新動向を紹介する。