連載

ARMから見た7nm CMOS時代のCPU設計(11)〜回路の遅延時間を変動させるさまざまな要因:福田昭のデバイス通信(22)(2/2 ページ)

今回は、回路の遅延時間を左右する要因について紹介する。例えば、コンタクト抵抗、しきい電圧、電源電圧、温度などがある。しきい電圧と温度、電源電圧と温度が遅延時間に与える影響はかなり複雑だが、その対処法として、DVFS(Dynamic Voltage and Frequency Scaling)技術が挙げられる。

電源電圧と動作周波数を動的にスケーリング

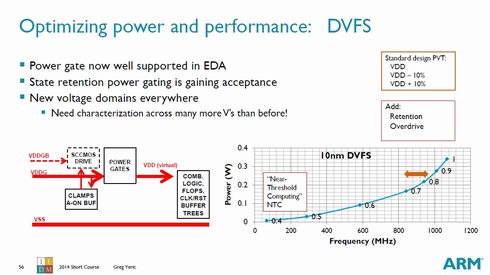

複雑化するPVTコーナーに対処しつつ、処理性能と消費電力の要求仕様を満足する有力な技術が、DVFS(Dynamic Voltage and Frequency Scaling)である。負荷や温度などの変動に応じて電源電圧と動作周波数を動的に制御する技術だ。

電源電圧を制御する最も単純な手法は、電源をオン・オフすることである。LSIを数多くのブロックに分割し、ブロックごとに電源をオン・オフする。このブロックを「電源ドメイン」と呼ぶ。もう少しきめ細かな制御になると、電源ドメインの電源電圧を動的に3通り(標準値、10%増の値、10%減の値)に変化させる。この3種類に加え、処理能力を一時的に高めるオーバードライブ電圧(さらに高い電源電圧)と、状態を維持するだけのリテンション電圧(さらに低い電源電圧)をオプションとして用意することもある。

電源ドメインとDVFS(Dynamic Voltage and Frequency Scaling)。左はパワーゲートによる電源制御のブロック図。右はDVFSの例。10nm世代の回路で電源電圧と動作周波数、消費電力の関係を示している(クリックで拡大) 出典:ARM

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

電源から電力を取り出す逆転の発想とは?

電源から電力を取り出す逆転の発想とは?

サーバ用電源では効率向上が強く求められている。富士通研究所は電源内部で発生する性質の異なった2種類の損失を防ぐために、それぞれ新規開発の技術を適用、94.8%の最高効率を実現した。特にトランジスタ内で生じるスイッチング損失を、一種の「回生回路」で再利用する取り組みが新しい。さまざまな機器の電源に応用できる。 ルネサスが0.2V対応電源ICを開発し、電波によるエネルギーハーベスティングシステムを実現

ルネサスが0.2V対応電源ICを開発し、電波によるエネルギーハーベスティングシステムを実現

ルネサス エレクトロニクスは、電波エネルギーから電気エネルギーを取り出し、マイコンや温度センサーを駆動させるシステムを開発した。0.2Vという低電圧を昇圧する技術などの技術を盛り込んだ。 FinFET以降の半導体製造技術はどう進む? IBMの見解

FinFET以降の半導体製造技術はどう進む? IBMの見解

「Common Platform Technology Forum」において、IBMが半導体製造技術の将来展望について発表を行った。液浸リソグラフィによるダブルパターニング技術やFD-SOI技術に加え、カーボンナノチューブ、シリコンフォトニクス、ナノワイヤーなどのキーワードを交えて半導体製造の将来像や課題などが示された。 14nm FinFETへの移行は「難しい決断だった」――サムスン

14nm FinFETへの移行は「難しい決断だった」――サムスン

Samsung Electronics(サムスン電子)の最新スマートフォン「Galaxy S6」には、14nm FinFETを適用したプロセッサが搭載されている。同社は、14nm FinFETの生産量において、Intelに次ぐ第2位のポジションを確保したい考えだ。Samsung Semiconductorの幹部は、14nmプロセスへの移行を決断するのは、たやすいことではなかったと振り返る。 TSMC、16nm FinFETのリスク生産を開始

TSMC、16nm FinFETのリスク生産を開始

TSMCが16nmプロセスを適用したFinFETのリスク生産を開始した。開発スケジュールは予定よりも早く進んでいるようだ。今後は、AppleやQualcommなどが、新しい世代のFinFETの製造を、TSMCとSamsung Electronicsのどちらにどの程度発注していくのかが注目される。