夞楬媄弍偺拲栚榑暥乣僾儘僙僢僒丄儊儌儕丄僶僀僆偺嵟怴僠僢僾丗VLSI僔儞億僕僂儉 2015 僾儗價儏乕乮4乯乮1/3 儁乕僕乯

崱夞徯夘偡傞偺偼丄崅惈擻僾儘僙僢僒丄16nm FinFET傪揔梡偟偨楢憐儊儌儕丄1600枩夋慺偺3師尦愊憌CMOS僀儊乕僕僙儞僒乕側偳偱偁傞丅僾儘僙僢僒偱偼丄僋儘僢僋暘攝媄弍傗丄Intel偺乽Broadwell乿偵娭偡傞榑暥偵偮偄偰愢柧偑偁偭偨丅

儘僕僢僋丄儊儌儕丄傾僫儘僌偺拲栚榑暥傪徯夘

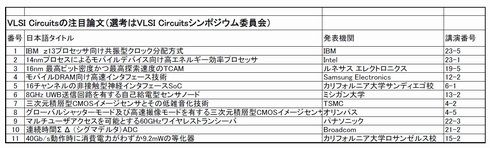

丂慜夞偼2015擭4寧20擔偵奐嵜偝傟偨曬摴婡娭岦偗愢柧夛偐傜丄夞楬媄弍偺尋媶惉壥偑斺業偝傟傞乽Symposium on VLSI Circuits乿乮VLSI Circuits僔儞億僕僂儉乯偺奣梫傪愢柧偟偨丅崱夞偼丄摨僔儞億僕僂儉埾堳夛偑慖傫偩拲栚榑暥傪偛徯夘偡傞丅僾儘僌儔儉埾堳挿傪柋傔傞杮懞恀恖乮傕偲傓傜丒傑偝偲乯巵乮杒奀摴戝妛乯偑11審偺拲栚榑暥偲偦偺梫揰傪愢柧偟偨丅

丂徯夘偝傟偨偺偼丄崅惈擻僾儘僙僢僒丄崅惈擻儊儌儕丄僶僀僆儊僨傿僇儖偍傛傃僙儞僒乕丄3師尦愊憌宆僀儊乕僕僙儞僒乕丄崅懍丒崅廃攇捠怣僠僢僾丄崅惈擻傾僫儘僌僨僕僞儖曄姺婍乮A-D曄姺婍乯偺尋媶奐敪惉壥偱偁傞丅

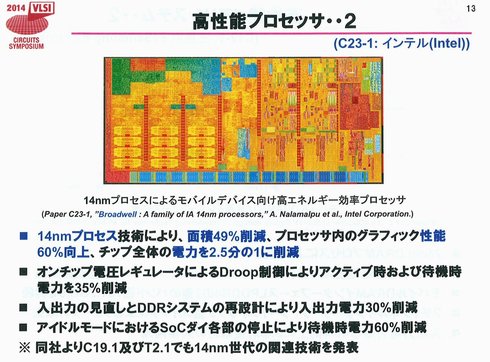

儌僶僀儖岦偗嵟怴僾儘僙僢僒乽Broadwell乿偺奣梫

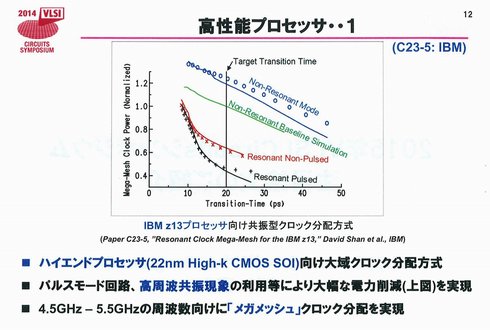

丂巒傔偵杮懞巵偼丄崅惈擻僾儘僙僢僒媄弍偵娭偡傞2審偺榑暥傪愢柧偟偨丅1審偼丄IBM偑奐敪偟偨嵟怴儊僀儞僼儗乕儉乽z13乿岦偗儅僀僋儘僾儘僙僢僒偺僋儘僢僋暘攝媄弍偵娭偡傞榑暥偱偁傞丅乽z13乿岦偗儅僀僋儘僾儘僙僢僒偺僋儘僢僋廃攇悢偼4.5GHz乣5.5GHz偲偒傢傔偰崅偔丄僋儘僢僋暘攝夞楬偵傛傞徚旓揹椡偑柍帇偱偒側偄悈弨偵戝偒偔側傞丅IBM偼僷儖僗儌乕僪夞楬偲崅廃攇嫟怳尰徾偺棙梡偵傛偭偰僋儘僢僋偺徚旓揹椡傪敿暘埲壓偵嶍尭偟偨丅

丂傕偆1審偼丄Intel偑奐敪偟偨嵟怴偺儅僀僋儘僾儘僙僢僒乽Broadwell乿偵娭偡傞島墘偱偁傞丅儌僶僀儖岦偗偵僄僱儖僊乕岠棪傪嵟揔壔偟偨丅戞2悽戙偺僆儞僠僢僾揹埑儗僊儏儗乕僞夞楬偵傛偭偰戞1悽戙偵斾傋偰摦嶌帪徚旓揹椡偲懸婡帪徚旓揹椡傪35亾嶍尭偡傞偲偲傕偵丄3師尦僀儞僟僋僞慺巕傪嵦梡偡傞偙偲偱僷僢働乕僕偺岤傒傪30亾尭傜偟偨丅慡懱偱偼22nm媄弍偺僾儘僙僢僒偵斾傋偰僌儔僼傿僢僋僗惈擻傪60亾崅傔傞偲偲傕偵丄徚旓揹椡傪2.5暘偺1偵壓偘偰偄傞丅

Copyright © ITmedia, Inc. All Rights Reserved.