回路技術の注目論文〜プロセッサ、メモリ、バイオの最新チップ:VLSIシンポジウム 2015 プレビュー(4)(2/3 ページ)

今回紹介するのは、高性能プロセッサ、16nm FinFETを適用した連想メモリ、1600万画素の3次元積層CMOSイメージセンサーなどである。プロセッサでは、クロック分配技術や、Intelの「Broadwell」に関する論文について説明があった。

次世代モバイルDRAM向けの高速インタフェース

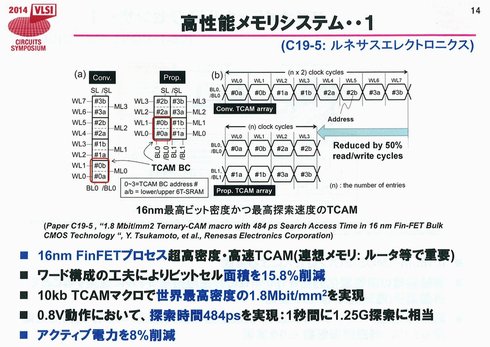

続いて、高性能メモリ技術に関する2件の論文を紹介した。1件は、ルネサス エレクトロニクスが開発した連想メモリ(TCAM)に関する講演である。16nmのFinFETプロセスを駆使することで、TCAMとしては最高の記憶密度である1.8Mビット/mm2を達成した。探索速度は1.25G探索/秒で、過去最高の探索速度を実現したとする。

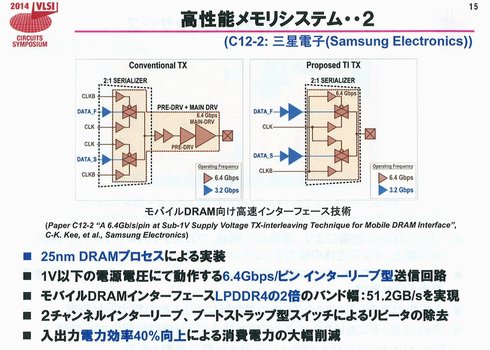

もう1件は、次世代モバイルDRAM向けの高速インタフェース技術に関する講演である。Samsung Electronicsが発表する。最新世代のモバイルDRAMである「LPDDR4 DRAM」の2倍に相当するデータ転送速度(バンド幅)を達成した。ピン当たりのデータ転送速度は6.4Gbit/秒と高い。25nmのDRAMプロセスで実装した。

16チャンネルの非接触型神経インタフェースSoC

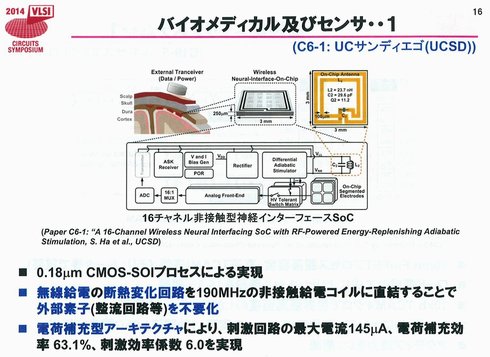

それから、バイオメディカルとセンサーに関する2件の論文を紹介した。1件は、カリフォルニア大学サンディエゴ校が開発した、16チャンネルの非接触型神経インタフェースSoCの技術内容である。生体の組織に埋め込んで神経に刺激を与えることを想定して開発した。外部のトランシーバ回路とは、無線でデータ通信と電力供給の両方をやり取りする。電力供給は190MHzの高周波無線で実施する。

もう1件は、体積が10.6mm3と小さく、外付け部品が不要の無線センサーノードに関する講演である。ミシガン大学が開発した。太陽電池と蓄電池によって電源を賄う。データ送信用の8GHz帯UWB送信回路とアンテナ、プログラミング用光受信回路を備える。他にはマイクロコントローラとメモリを搭載した。

Copyright © ITmedia, Inc. All Rights Reserved.