夞楬媄弍偺拲栚榑暥乣僾儘僙僢僒丄儊儌儕丄僶僀僆偺嵟怴僠僢僾丗VLSI僔儞億僕僂儉 2015 僾儗價儏乕乮4乯乮3/3 儁乕僕乯

崱夞徯夘偡傞偺偼丄崅惈擻僾儘僙僢僒丄16nm FinFET傪揔梡偟偨楢憐儊儌儕丄1600枩夋慺偺3師尦愊憌CMOS僀儊乕僕僙儞僒乕側偳偱偁傞丅僾儘僙僢僒偱偼丄僋儘僢僋暘攝媄弍傗丄Intel偺乽Broadwell乿偵娭偡傞榑暥偵偮偄偰愢柧偑偁偭偨丅

1600枩夋慺偺3師尦愊憌僀儊乕僕僙儞僒乕

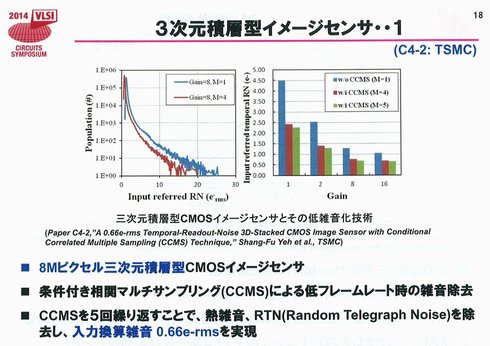

丂偝傜偵丄3師尦愊憌宆CMOS僀儊乕僕僙儞僒乕偵娭偡傞2審偺奐敪惉壥傪徯夘偟偨丅1審偼丄TSMC偑奐敪偟偨800枩夋慺乮僺僋僙儖乯偺掅嶨壒僀儊乕僕僙儞僒乕偱偁傞丅僒儞僾儕儞僌傪5夞孞傝曉偡偙偲偵傛偭偰擬嶨壒偲RTN乮Random Telegraph Noise乯傪彍嫀偟偨丅擖椡姺嶼嶨壒揹巕悢偼0.66揹巕乮rms抣乯偲彫偝偄丅

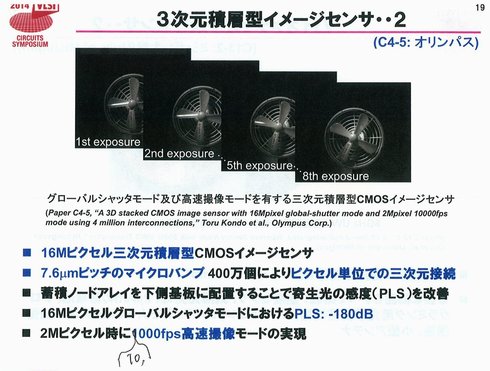

丂傕偆1審偼丄僆儕儞僷僗偑奐敪偟偨1600枩夋慺偺3師尦愊憌宆僀儊乕僕僙儞僒乕偱偁傞丅400枩8960屄偺儅僀僋儘僶儞僾偵傛偭偰夋慺扨埵偱偺3師尦愙懕傪幚尰偟偨丅嶣憸婡擻偱偼丄捠忢偺僌儘乕僶儖僔儍僢僞乮慡夋慺堦妵業岝乯儌乕僪偺懠丄200枩夋慺傪1枩僼儗乕儉/昩偲偒傢傔偰崅偄懍搙偱嶣塭偡傞崅懍嶣憸儌乕僪傪旛偊傞丅

挻崅懍柍慄LAN岦偗60GHz儈儕攇僩儔儞僔乕僶

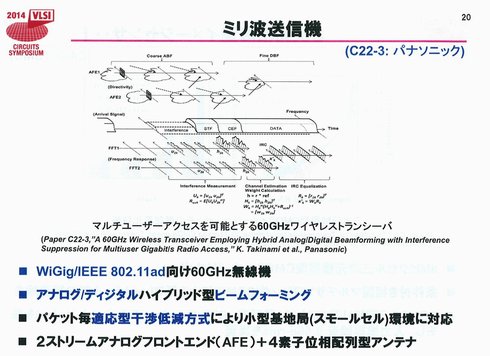

丂偙偺懠丄捠怣暘栰偲儈僢僋僗僪僔僌僫儖暘栰偱崌寁3審偺拲栚榑暥傪徯夘偟偨丅嵟弶偺1審偼丄僷僫僜僯僢僋偑奐敪偟偨60GHz偺儈儕攇僩儔儞僔乕僶偱偁傞丅IEEE 802.11ad/WiGig岦偗丅儅儖僠儐乕僓偵傛傞傾僋僙僗偑壜擻偱偁傞丅傾僫儘僌偲僨僕僞儖偺僴僀僽儕僢僪宆價乕儉僼僅乕儈儞僌偵傛偭偰怣崋娫偺姳徛傪梷惂偟偨丅

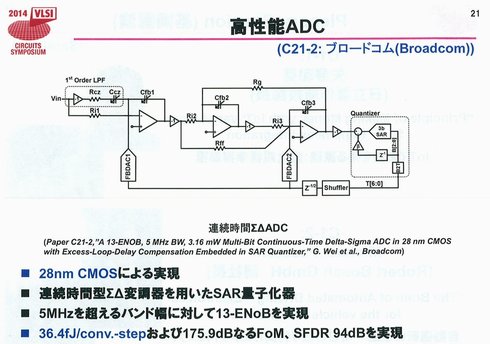

丂師偺1審偼丄Broadcom偑奐敪偟偨崅惈擻傾僫儘僌僨傿僕僞儖乮A-D乯曄姺夞楬偱偁傞丅桳岠價僢僩悢乮ENOB乯偼13價僢僩偲崅偄丅僶儞僪暆偼5MHz丅徚旓揹椡偼3.16mW偲掅偄丅3價僢僩偺楢懕帪娫宆儼儮曄挷婍傪嵦梡偟偨SAR乮拃師斾妑乯検巕壔婍傪嵹偣偰偄傞丅帋嶌偟偨夞楬偺SFDR乮僗僾儕傾僗僼儕乕僟僀僫儈僢僋儗儞僕乯偼94dB偲崅偄丅惢憿媄弍偼28nm偺CMOS媄弍丅

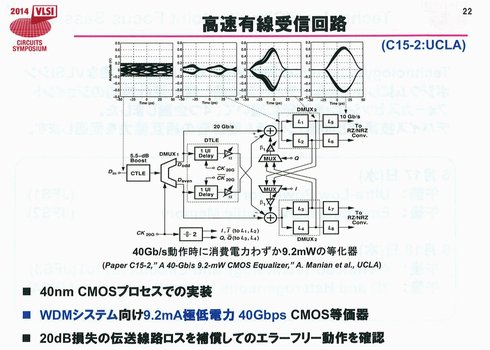

丂嵟屻偺1審偼丄僇儕僼僅儖僯傾戝妛儘僒儞僛儖僗峑偑奐敪偟偨崅懍偐偮掅揹椡偺桳慄捠怣摍壔婍乮僀僐儔僀僓乯夞楬偱偁傞丅40G價僢僩/昩偱摦嶌偟偨偲偒偺徚旓揹椡偼9.2mW偲掅偄丅攇挿暘妱懡廳曽幃偺岝僼傽僀僶捠怣岦偗丅惢憿媄弍偼45nm偺CMOS媄弍丅

Copyright © ITmedia, Inc. All Rights Reserved.

娭楢婰帠

乽宱尡偱愝寁偡傞偲幐攕偡傞乿丄儖僱僒僗偑採帵偡傞16nm FinFET SRAM偺壽戣

乽宱尡偱愝寁偡傞偲幐攕偡傞乿丄儖僱僒僗偑採帵偡傞16nm FinFET SRAM偺壽戣

儖僱僒僗 僄儗僋僩儘僯僋僗偼丄16nm FinFET僾儘僙僗傪梡偄偰SRAM傪帋嶌偟偨偲敪昞偟偨丅僾儗乕僫宆MOSFET傪巊偆応崌偵斾傋偰掅偄摦嶌揹埑偱崅懍撉傒弌偟偵惉岟偟偰偄傞偑丄堦曽偱FinFET偲丄旝嵶壔僾儘僙僗傪梡偄偨偙偲偵傛傞壽戣傕憹偊偰偄傞丅 CMOS僀儊乕僕僙儞僒乕偑堷偭挘傞3師尦愊憌媄弍

CMOS僀儊乕僕僙儞僒乕偑堷偭挘傞3師尦愊憌媄弍

僠僢僾傪愊憌偟丄TSV乮僔儕僐儞娧捠揹嬌乯側偳偱愙懕偡傞3師尦IC媄弍丅CMOS僀儊乕僕僙儞僒乕偱傕丄3師尦壔偑恑傫偱偄傞丅 60GHz懷捠怣偺惃椡恾丄Wi-Fi Alliance偲WiGig偺崌暪偱偳偆曄傢傞丠

60GHz懷捠怣偺惃椡恾丄Wi-Fi Alliance偲WiGig偺崌暪偱偳偆曄傢傞丠

Wireless Gigabit Alliance乮WiGig乯偼丄60GHz懷傪棙梡偡傞柍慄捠怣偺婯奿嶔掕偵庢傝慻傫偱偒偨丅Silicon Image傕丄60GHz懷偺柍慄捠怣偱撈帺偺婯奿傪庤妡偗偰偄傞丅Wi-Fi Alliance偲WiGig偼2013擭1寧偵丄崌暪偡傞偙偲傪敪昞偟偨偑丄偙傟偵傛偭偰60GHz懷偺柍慄捠怣婯奿偺乬惃椡恾乭偵曄壔偼偁傞偺偩傠偆偐丅 悽奅傪曪傓揹巕偺恄宱栐 乗乗 乬儌僲偺僀儞僞乕僱僢僩乭偑旈傔傞壜擻惈

悽奅傪曪傓揹巕偺恄宱栐 乗乗 乬儌僲偺僀儞僞乕僱僢僩乭偑旈傔傞壜擻惈

奺庬僙儞僒乕抂枛偐傜壠揹丄僀儞僼儔婡婍傑偱丄偁傜備傞儌僲偵捠怣婡擻傪慻傒崬傫偱僱僢僩儚乕僋壔偡傞丄偄傢備傞乬儌僲偺僀儞僞乕僱僢僩乭偼丄偙偺抧媴偵挘傝弰傜偝傟傞僄儗僋僩儘僯僋僗偺恄宱栐偩丅偦偙偱懆偊偨朿戝側忣曬偐傜壙抣偺偁傞忣曬傪拪弌偡傟偽丄恖椶偵偲偭偰偝傑偞傑側壽戣傪夝寛偡傞桳椡側庤抜偵側傞偩傠偆丅 摢奧撪偺揹嬌傪柍慄偱儌僯僞儕儞僌丄偰傫偐傫帯椕偺晧扴尭傊

摢奧撪偺揹嬌傪柍慄偱儌僯僞儕儞僌丄偰傫偐傫帯椕偺晧扴尭傊

僗僀僗 儘乕僓儞僰楢朚岺壢戝妛乮EPFL乯偼丄偰傫偐傫偺帯椕岦偗偵丄擼撪妶摦傪柍慄偱儌僯僞儕儞僌偡傞媄弍傪奐敪拞偩丅揹嬌偲傾儞僥僫丄RF僠僢僾傪摢奧撪偵杽傔崬傒丄揹帴桿摫偱揹椡傪嫙媼偟側偑傜丄揹嬌偺僨乕僞傪柍慄偱儌僯僞儕儞僌偡傞丅摢奧撪偵杽傔崬傫偩揹嬌傪婰榐憰抲偵桳慄偱愙懕偟偰偄傞尰嵼偺庤弍傪丄戝偒偔曄偊傞壜擻惈偑偁傞丅