独自低消費電力プロセスの40nm版、2017年量産へ:三重富士通セミコン、IoTによる需要拡大に備え

三重富士通セミコンダクターは2015年12月16〜18日の会期で開催されている展示会「WORLD OF IOT」(併催:SEMICON Japan2015)で、独自トランジスタ構造「DDC(Deeply Depleted Channel)トランジスタ」を使用した低消費電力CMOSプロセス技術に関する展示を実施。同技術を用いた40nmプロセスによる受託量産を2017年から開始する方針を明かした。

半導体受託製造企業である三重富士通セミコンダクターは2015年12月16〜18日の会期で開催されている展示会「WORLD OF IOT」(併催:SEMICON Japan2015/会場:東京ビッグサイト)で、独自のトランジスタ「DDC(Deeply Depleted Channel)トランジスタ」を使用した低消費電力CMOSプロセス技術に関する展示を実施している。IoT(モノのインターネット)化の進展により、拡大が予想される低消費電力デバイス需要を取り込むため、既に量産中の55nm世代版での受注活動と並行し、40nm世代版の開発を進め、2017年から量産を実施する予定だとした。

従来プロセスよりも50%消費電力を削減

三重富士通セミコンの低消費電力プロセスの核となるDDCトランジスタは、電源電圧をより低く抑えることを可能にするトランジスタだ。昨今の微細プロセスでは、トランジスタの不純物ばらつきに起因したしきい値電圧のばらつきが大きくなり、プロセスルールを微細化しても、思うように電源電圧を下げることができなかった。

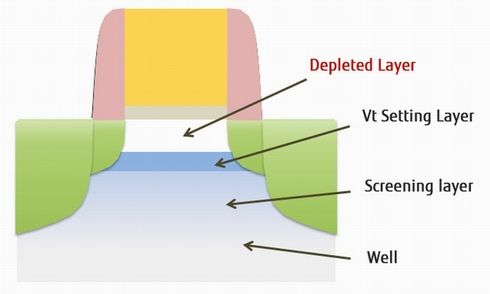

それに対し、DDCトランジスタはプレーナー型CMOS構造のチャネル部分に不純物濃度の異なる複数の層を形成することにより、不純物による製造ばらつきを低減する。これにより、しきい値電圧のバラツキを抑えられ、結果として電源電圧を下げられるようになる。また、チップごとのプロセスばらつきに応じて最適なボディバイアスを供給するABB(Adaptive Body Bias)制御を適用するといった工夫も実施。従来の製造プロセスと比較し、同一動作速度であれば、「消費電力を約50%削減したデバイスが製造できる」(同社)という。

DDCトランジスタのIPを買い取り、開発を加速中

このDDCトランジスタは、米SuVoltaが開発したもの。三重富士通セミコンでは、DDCトランジスタを核にした低消費電力CMOS技術「PowerShrink」のライセンスをSuVoltaから取得し、55nmプロセスに適用し2013年9月から量産を実施。PowerShrinkを唯一、適用した製造ラインという強みを打ち出しつつ、低消費電力ニーズの強いデバイスの製造受託につなげてきた。

そうした中で三重富士通セミコンは2015年4月に、SuVoltaからDDCトランジスタを含むPowerShrink関連技術の知的財産権を取得。DDCトランジスタ/PowerShrinkを“独自技術”として自社で直接、開発する体制へと切り替えた。

“三重富士通セミコン独自技術・DDCトランジスタ/PowerShrink”としての開発は、55nm世代でのさらなる低消費電力化やフラッシュメモリとの混載化を進めているという。さらに、2016年から量産を予定している40nmプロセスへの適用に向けた開発にも着手し「2017年から40nmプロセスでのDDCトランジスタを用いたデバイスの量産を実施する予定」(説明員)とした。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

IoTを原動力に復活狙う日本半導体産業――SEMICON Japan2015

IoTを原動力に復活狙う日本半導体産業――SEMICON Japan2015

マイクロエレクトロニクス製造サプライチェーンの国際展示会「SEMICON Japan2015」が、2015年12月16〜18日の3日間、東京ビッグサイトで開催される。IoT向け半導体需要の拡大で注目を集めているのが200mmウェハーファブの有効活用である。日本半導体産業の復活に期待がかかる。 従来比1/30のコストでライン構築できる接合技術

従来比1/30のコストでライン構築できる接合技術

コネクテックジャパンは、「SEMICON JAPAN 2015」に、ダメージフリー接合技術とデスクトップ型フリップチップボンダーを日本で初めて展示すると発表した。 300mmウエハー対応のバンプ形成技術「IMS」

300mmウエハー対応のバンプ形成技術「IMS」

JSRと日本アイ・ビー・エム、千住金属工業の3社は2015年12月9日、半導体の高密度実装を可能にするはんだバンプの形成技術「IMS」を発表した。同技術は、2015年12月16〜18日に東京ビッグサイトで開催される「SEMICON JAPAN 2015」で展示される予定である。 IoT市場を支える4〜8インチ対応のFEB測長装置

IoT市場を支える4〜8インチ対応のFEB測長装置

日立ハイテクノロジーズは2015年11月、4〜8インチウエハーサイズに対応した高分解能FEB(Field Emission Beam)測長装置「CS4800」を開発したと発表した。CS4800は、2015年12月16〜18日に東京ビッグサイトで開催される「SEMICON JAPAN 2015」で展示される予定だ。