STT-MRAMでSRAM比1/10以下の消費電力を達成:東芝など「全メモリで世界最高電力性能」

東芝と東京大学は2016年2月1日、「あらゆる種類のメモリと比べ世界最高の電力性能」というMRAMを開発したと発表した。

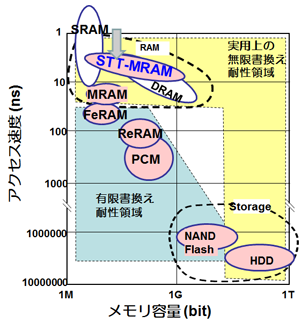

東芝と東京大学は2016年2月1日、コンピュータのキャッシュメモリとして使用できる高速性能を備えながら、SRAMに比べ消費電力を10分の1以下に抑えた容量4Mビット級のスピン注入磁化反転方式の磁気抵抗メモリ(以下、STT-MRAM*))を開発したと発表した。東芝などでは、「あらゆる種類のメモリと比べ世界最高の電力性能」とする。

*)STT-MRAM:Spin Transfer Torque-Magnetic Random Access Memory

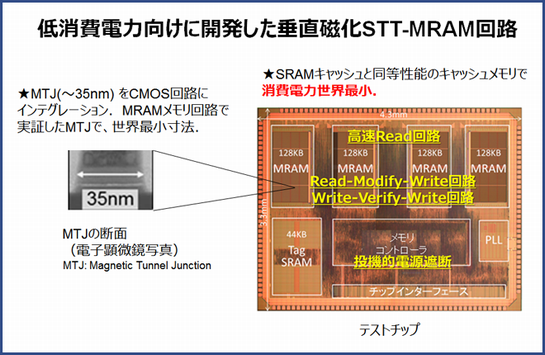

東芝と東大情報理工学系研究科教授中村宏氏らのグループが開発したSTT-MRAMは、65nm世代のシリコントランジスタに混載した容量4MビットクラスのMRAM。アクセス時間は3.3ナノ秒を実現するとともに、SRAMと比べて消費電力を10分の1以下に抑えている。

MRAMは、揮発性メモリであるSRAMと同様の高速性能を誇る次世代型不揮発メモリとして知られている。不揮発であるため、記憶保持用電力を必要とせず、SRAMなど揮発性メモリよりも消費電力を抑えられる利点がある。ただ、実際には、MRAMのメモリ制御回路部が消費する電力が大きく、制御回路を含めたメモリ全体としての消費電力抑制効果は大きくなかった。

こうした課題に対し、東芝と東大のグループは、メモリ制御回路部をノーマリーオフ動作状態に近づけるために、100ナノ秒以下で高速に電力遮断/復帰が行える回路を開発。メモリ動作状態に応じて動作に必要な部分以外は高速で電源遮断できるようにし、高速性能と電力性能の両立を狙った。

試作チップを用いて測定を行ったところ、キャッシュメモリアクセスの平均待機時間は約30ナノ秒よりも短い最速22ナノ秒での電源遮断後から復帰までの動作を確認したとする。

さらに、メモリのデータを1度確認して不要な書き込みを止めることで書き込み動作の消費電力を削減する技術を適用。電源を遮断できる時間をできるだけ長くするために、メモリアクセスパターンをモニターして、次のアクセスパターンを高い正解率で予測するアルゴリズムも開発し、SRAM比10分の1以下の消費電力でのMRAM動作を実現した。

なお、開発したSTT-MRAMの技術開発は、新エネルギー・産業技術総合開発機構(NEDO)の「ノーマリオフコンピューティング基盤技術開発プロジェクト」として行われているもの。今回の技術開発成果については、2016年2月1日から米国で行われている半導体回路国際会議「ISSCC 2016」で発表される。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

着実な進展を見せるMRAM技術

着実な進展を見せるMRAM技術

今回から、カンファレンス最終日のセッションを紹介する。セッション26は、「MRAM、DRAMとSRAM」をテーマに講演が進んでいく。MRAMについては計4件の論文発表があり、例えばQualcomm Technologiesらは、40nmルールのCMOSロジックに埋め込むことを想定したSTT-MRAM技術を報告する。 電圧トルクMRAMの安定動作を実証、評価法も開発

電圧トルクMRAMの安定動作を実証、評価法も開発

産業技術総合研究所の塩田陽一研究員は、電圧書込み方式不揮発性メモリが安定動作することを実証するとともに、書込みエラー率の評価方法を開発した。電圧トルクMRAMの実用化に向けた研究に弾みがつくものとみられる。 ニッチ用途の域を出ないMRAM、普及の鍵はコストと記録密度

ニッチ用途の域を出ないMRAM、普及の鍵はコストと記録密度

幅広い用途でDRAMやSRAMの置き換えになると予想されているMRAM(磁気抵抗メモリ)。産業用途を中心に採用が進んでいるが、普及が加速するにはまだ時間が必要なようだ。 産総研、TMR素子の記憶安定性を約2倍に向上

産総研、TMR素子の記憶安定性を約2倍に向上

産業技術総合研究所(産総研)の薬師寺啓氏は、スピントルク書込型磁気ランダムアクセスメモリ(STT-MRAM)に用いられる垂直磁化トンネル磁気抵抗(TMR)素子の記憶安定性を従来の2倍に向上させることに成功した。素子サイズが20nm以下の大容量SST-MRAMを実現することが可能となる。