自動運転向けの故障検出機能、16nmの9コアSoCに:ルネサスが「ISSCC 2016」で発表(2/2 ページ)

ルネサス エレクトロニクスは、自動運転向けの車載コンピューティングシステム用に、ハードウェアの故障を予測・検出する技術を開発した。さらにそれを、16nm FinFETプロセスを用いた9コアSoC(System on Chip)に実装し、「ISSCC 2016」でデモを披露した。

機能ブロック別のセルフテストが可能に

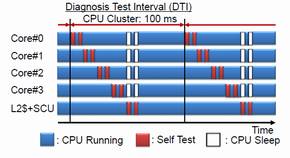

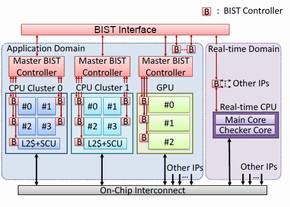

セルフテスト機構のブロック図。図版中の「BIST」は、「ビルトイン・セルフテスト(Built-In Self Test)」で、「B」はBIST用コントローラを指している(クリックで拡大) 出典:ルネサス

まず、CPU/GPUの機能ブロック別にセルフテスト機構を実装し、それらの機構を統合制御するコントローラも実装することで、機能ブロック別のセルフテストや、1種類のテストを複数回に分割して実行する機能を開発した。

これにより、4つのCPUで構成されるCPUクラスタのうち、特定のCPUのみセルフテストを実行し、あとの3つのCPUでプログラムを実行する、といったことができる。

特定のCPU/GPUで実行するセルフテストを複数回に時分割することで、例えば音声処理に求められる処理中断時間2ミリ秒以下という要求に対応することが可能になったという。

このように、安全機能の中断時間を最小化することで、大規模SoCにおいても、機能安全規格「ISO 26262 ASIL B」で要求される診断カバー率(Diagnostic Coverage)を実現できるとしている。

瞬間的な電圧降下を予測

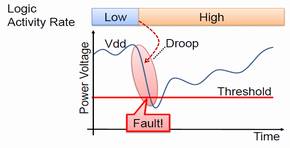

ハードウェア障害を抑止する機構については、次の3つを開発した。

1)電圧検知機構:電圧差によって伝搬時間が変化する可変遅延回路と、基準クロックとの時間差をデジタル値に変換する変換器を組み合わせたもの。2GHzで動作する

2)電圧降下予測機構:電圧検知機構で得た情報を基に、4サイクル先の電圧値を予測。予測値が、あらかじめ設定しておいた閾値を下回る場合は、3)の高機能クロック制御機構に制御を要求する

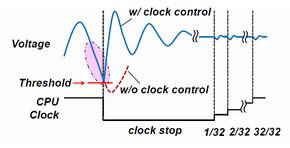

3)高機能クロック制御機構:クロックゲーティング回路とクロック分周器を組み合わせ、2)の制御要求が届いたら、即座に制御対象へのクロック供給を停止して、電圧降下を抑止する。クロック供給停止後は、停止前よりも低い周波数から、1/32ステップで周波数を回復させることで、クロック供給の再開に伴う電圧降下を最小限に抑える

これらの3つの機構を組み合わせることで、瞬間的な電圧降下を事前に検知し、それによって生じるハードウェア障害を抑止することが可能になったという。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Google CarにもV2V技術は不可欠だ

Google CarにもV2V技術は不可欠だ

このほど、Google(グーグル)とDelphi Automotive(デルファイ)の自動運転車が路上で、衝突寸前のニアミスを起こしていたことが判明した。人為的ミスの存在しない自動運転車同士のニアミスの一因は、V2V(車車間)通信技術を搭載していなかった点にあるだろう。 高性能A/D変換器の開発成果と本音トークのパネル討論会

高性能A/D変換器の開発成果と本音トークのパネル討論会

セッション15では、Analog Devices(ADI)が発表する、入力帯域幅が465MHzと極めて広いΔ-Σ方式のA/D変換器などに注目したい。2016年2月1日と2日の夜に行われる、パネル討論会も興味深い。「無線回路を20nm未満に微細化する必要はあるのか」や、「2000年代の回路設計で最も素晴らしい瞬間」などが討論のテーマだ。パネリストたちの熱い本音トークが聞けることを期待したい。 自動運転の実現はまだ遠く、トヨタがCESで語る

自動運転の実現はまだ遠く、トヨタがCESで語る

トヨタ自動車は「2016 International CES」で、人工知能の研究開発のための新会社「Toyota Research Institute」について説明するとともに、自動運転の展望について語った。 ルネサスが“クルマ”を売る!? その真意とは

ルネサスが“クルマ”を売る!? その真意とは

ルネサス エレクトロニクスは米国で開催した「DevCon 2015」で、同社のADAS(先進運転支援システム)向けの最新SoCなどを搭載した自動車を披露した。実は、この自動車は、自動運転車などの開発を促進すべく同社が発表した“プラットフォーム”である。