Intel、10nmプロセスでは新技術は導入せず:「ISSCC 2016」で“ポストCMOS”を語る

Intelは「ISSCC 2016」でムーアの法則の維持と“ポストCMOS”について講演し、10nmプロセスでは新しい技術は導入しないことを断言した。

「ムーアの法則は非常に息が長いが、一般的なCMOS技術はそうでもないようだ」――。Intelの技術製造部門担当ゼネラルマネジャーを務めるWilliam Holt氏は、米国サンフランシスコで開催中の「ISSCC 2016」(2016年1月31日〜2月4日)において、半導体チップメーカー関係者が中心の聴衆に向け、自身の考えを語った。

Holt氏は、会場に集まった約3000人の聴衆を前に、「ムーアの法則については、トランジスタ1個当たりのコスト削減に注力していくことで、その経済的な合理性を維持できる。しかし、“ポストCMOS”では、あらゆるものが変化し、コンピュータアーキテクチャでさえも変わるのではないだろうか」と述べている。

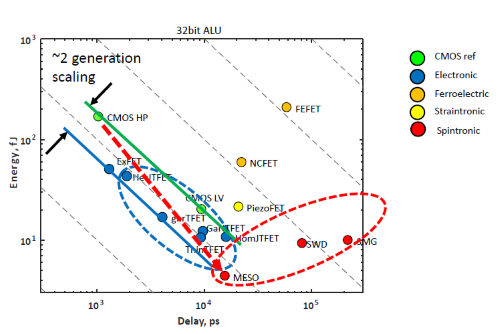

同氏は、半導体メーカーが、多種多様な“ポストCMOS”技術の中から、どのタイミングでどの技術を選ぶことになるのかについては、自身の考えを明かそうとはしなかった。このような新技術としては、トンネルFET(TFET)や、強誘電体FET、スピントロニクス、新しいIII-V族材料など、幅広い技術が挙げられる。

10nmプロセスでは、新技術は採用しない

Holt氏は、「Intelは、10nmプロセス技術において新技術を採用するつもりはない。当社は現在、次世代プロセッサの試作において10nmプロセスの適用を進めているところだ。エンジニアは一般的に、可能な限りCMOS技術を使い続けようとする。長期的な視点で見ると、半導体チップには、既存のCMOS技術と他のさまざまな技術とを組み合わせた、“ハイブリッド型”の技術が適用されることになるだろう」と主張する。

同氏は、「同じウエハー上にCMOSトランジスタと、さまざまなメリットを実現する他の機能を最適化して作り込むといったような、“融合型”の工程が採用されるのではないだろうか」と述べる。

また同氏は、半導体業界が今後10年の間に新たな道を切り開いていくことができるよう、大規模な研究開発の取り組みが行われていることについて、前向きに評価している。

さらに、「どのポストCMOS技術が最も優れていて、最初に採用されることになるのかは不明だ。しかし、選択肢が広がっていることから、今後数年の間にさまざまなチャンスがもたらされ、製造に不可欠な飛躍的進歩が実現するだろう。いかにして最適な製造手法を見つけ出すかが、今後の課題だ」と語った。

ポストCMOSの最大の課題は、動作速度か

今のところ、ポストCMOSとされている代替技術は全て、最大の懸念事項である消費電力の低減を実現することが可能である。一方で最大の問題は、CMOS回路と比べて動作速度が大幅に低下するという点だ。

Holt氏はこの問題について、差し迫った電力需要に対応するためにバイポーラ技術からCMOS技術へと移行した当時も、新たな複雑性が生じたことを、一例として取り上げている。

同氏は、「半導体業界は今後も、トランジスタ当たりの消費電力とコストの削減に注力していく必要がある。業界ではこれまでに、トランジスタ当たりのコストを30%削減してきたが、Intelは22/14nmプロセス技術において、それをわずかに上回るコスト削減に成功した。過去数世代における新しいプロセス技術の開発コストが、従来の10%増から、30%にまで増加したという事実にもかかわらずだ」と繰り返し主張した。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

終えん間近のムーアの法則、“ポストCMOS”の技術を模索へ

終えん間近のムーアの法則、“ポストCMOS”の技術を模索へ

米国で開催されたシンポジウム「IEEE Technology Time Machine(TTM)2014」では、“ポストCMOS”の技術について議論が交わされた。注目されているのは、量子コンピュータ、ビッグデータ、カーボンナノチューブ、人間の脳(シナプス)をまねた技術などである。 ムーアの法則、50年をたどる

ムーアの法則、50年をたどる

1965年、IntelのGordon Moore(ゴードン・ムーア)氏が雑誌に掲載したトランジスタに関する予見は、「ムーアの法則」として半導体技術の発展の大きな原動力となった。ムーアの法則によってトランジスタがどれほど進化してきたのか。50年を振り返ってみる。 IBMが7nm試作チップを発表、Intelに迫る勢い

IBMが7nm試作チップを発表、Intelに迫る勢い

IBM Researchが、EUV(極端紫外線)リソグラフィとSiGe(シリコンゲルマニウム)チャネルを使用した7nmプロセス試作チップを発表した。IBM Researchはここ最近、最先端プロセスの研究開発成果の発表に力を入れていて、7nmプロセスの技術開発に自信を示してきたIntelに迫る勢いを見せている。 人間の脳が握る、デバイス低消費電力化の鍵

人間の脳が握る、デバイス低消費電力化の鍵

ウェアラブル機器に欠かせない要件の1つに、低消費電力がある。「第2回 ウェアラブルEXPO」のセミナーに登壇した日本IBMは、超低消費電力のコンピュータとして、人間の”脳”を挙げ、IBMが開発中の「超低消費電力脳型デバイス」について語った。