CPUとメモリのアーキテクチャ:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(3)(2/2 ページ)

今回からは、「CPUのメモリに対する要求」について紹介していく。まずは、CPUのアーキテクチャがどのように変ってきたかを振り返りつつ、CPUのメモリに対する要求の変遷を見ていこう。

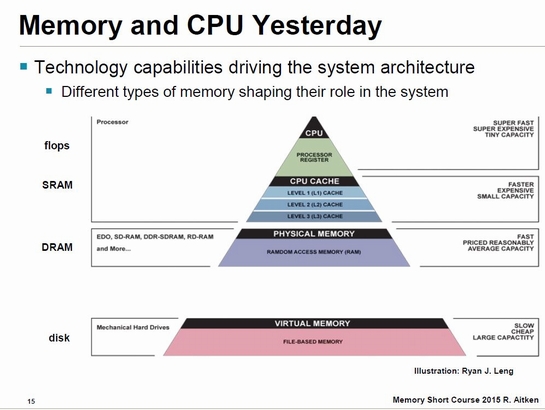

メモリ・アーキテクチャはピラミッド形の階層構造

CPUを搭載したシステムのメモリ・アーキテクチャは、正三角形あるいはピラミッド形をした図形の内部に水平な層を垂直方向に重ねた「階層構造」で説明することが多い。ピラミッドの高さはメモリの速度を、ピラミッドの幅はメモリの容量を定性的に表現している。ピラミッドの頂点に近いメモリは、高速だが小容量であり、ピラミッドの底辺に近いメモリは、低速だが大容量である。

過去のメモリ・アーキテクチャ、すなわちNANDフラッシュメモリが発明されて普及する以前のピラミッド構造を始めに説明しよう。ピラミッドの頂点であるCPUに最も近いメモリは、「レジスタ」である。レジスタはCPUに近いというよりは、CPUの内部に存在するというのが正しい。レジスタの中身(実現技術)はフリップフロップである。

レジスタのすぐ下層には、「キャッシュ」メモリが存在する。キャッシュは複数のメモリ階層で構成されていることが多い。最上層が「1次キャッシュ(L1:Level1 Cache)」、その次が「2次キャッシュ(L2:Level2 Cache)」となる。1次キャッシュと2次キャッシュを比べると、1次キャッシュが高速、2次キャッシュが大容量という違いがある。キャッシュの中身(実現技術)はSRAMである。

CPUのシリコンダイは、メモリ階層での頂点からキャッシュまでを内蔵していることが多い。言い換えると、キャッシュよりも下層のメモリは別のシリコンダイになる。

キャッシュの下層には、「主記憶」あるいは「システム・メモリ」と呼ぶ大容量メモリが位置する。「物理メモリ(Physical Memory)」と呼ぶこともある。主記憶の実現技術はふつう、DRAMである。

主記憶からさらに下のメモリ階層には「仮想メモリ(Virtual Memory)」が来る。仮想メモリの中身(実現技術)はハードディスク装置(HDD)である。HDDはDRAMに比べるとはるかに低速であるものの、記憶容量はDRAMに比べるとはるかに大きい。

(次回に続く)

⇒⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

システム設計の要諦は電力管理

システム設計の要諦は電力管理

今回から、2015年12月に開催された「IEDM2015」でARM Researchが講演した、メモリ技術の解説をお届けしよう。まずは、システム設計が抱える課題から紹介していきたい。 システム設計者を悩ませる制約条件

システム設計者を悩ませる制約条件

システム設計において、CPUコアはもはやそれほど重要ではない。大切なのは、メモリ、相互接続(配線)、消費電力、ソフトウェアである。ディスプレイを例に挙げ、最適なシステム・アーキテクチャの構築について説明しよう。 PCIeが今後の主流に

PCIeが今後の主流に

今回から始まるシリーズでは、SSDインタフェースの最新動向に焦点を当てて解説する。SSD関連のインタフェースは数多く存在するが、近年、採用が進んでいるのがPCIeだ。 ストレージの過去・現在・未来

ストレージの過去・現在・未来

磁気メディアや半導体メモリなどを使った「ストレージ」を解説する福田昭氏の新連載。ストレージ技術を中心に据えながら、ストレージに関する市場やビジネスにも触れていく。第1回は、HDDをフラッシュメモリやSSDと比較し、今後のストレージがどのような道をたどるのか、ヒントを示した。