連載

投機的プリフェッチとキャッシュの弱点:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(8)(2/2 ページ)

今回は、メモリアクセスの高速化手法である「投機的プリフェッチ(Speculative Prefetch)」の仕組みを解説する。これは、“次のアクション”を推測して、データをキャッシュにコピーするものだ。この他、キャッシュが抱える本質的な弱点についても触れておきたい。

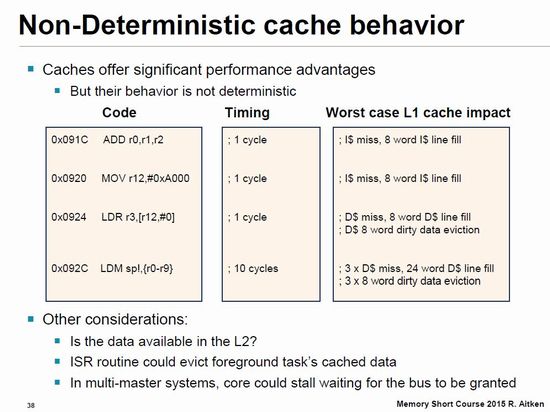

実行してみないとタイミングが決まらない

キャッシュの本質的な弱点は、実際に実行してみないと本当のタイミングが決まらないことだ。ヒット率が低く、キャッシュミスが発生したときの遅延時間が非常に長い場合は、キャッシュが存在することそのものが性能の低下を招くことすらある。例えば複数のアドレスにアクセスする多重ロード命令(LDM命令)でキャッシュミスが発生すると、CPUの待ち時間は長大なものになる。これまで述べてきたいくつかの工夫は、メモリアクセスがキャッシュにヒットすることで初めて、性能の向上をもたらす。

キャッシュの有効性を支えているのは、データの局所性である。局所性には時間的局所性(一度アクセスしたデータは近い将来に再度アクセスする)と空間的局所性(特定のアドレスにアクセスが集中)があり、キャッシュではこれらの両方の性質を利用する。従って、局所性の少ないアプリケーションでは、キャッシュが有効に働かないことがある。

この他、1次キャッシュでミスしたとしても、2次キャッシュでヒットするかミスするかによって、結果は大きく違う。また割り込みサービスルーチン(ISR)の発生は、キャッシュラインのデータを無駄にする可能性がある。そしてマルチマスターのシステムでは、CPUがバスを確保するまでの待ち時間が発生して性能を低下させる恐れが残る。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

IEDMで発表されていた3D XPointの基本技術(前編)

IEDMで発表されていた3D XPointの基本技術(前編)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。 IEDM開催スケジュールの全体像

IEDM開催スケジュールの全体像

今回からは、2015年12月に米国ワシントンD.C.で開催される、最先端電子デバイスの国際学会「IEDM 2015」のプレビューを紹介する。実は、ワシントンD.C.で開催されるIEDMは、今回が最後になる。 CPUアーキテクチャの基礎

CPUアーキテクチャの基礎

今回から、CPUアーキテクチャとメモリ・システムの関連について掘り下げていこう。まずは5段パイプラインアークテクチャを例に挙げ、メモリ・システムとの関連をみていく。 のぞいてみよう、マイコンの中!! ―― 複雑な演算も簡単な動作の繰り返し

のぞいてみよう、マイコンの中!! ―― 複雑な演算も簡単な動作の繰り返し

マイコンの中身って、どうなっているのでしょうか? どうやって複雑な演算を実行しているのでしょうか? その仕組みを知っておくと、いざマイコンを使う時にとても役立ちます。今回は、マイコンの内部の仕事の流れをつかんでください。