東工大、微細化でIGBTのオン抵抗を半減:3分の1スケーリングで実証

東京工業大学は、微細加工技術によりシリコンパワートランジスタの性能を向上させることに成功したと発表した。従来に比べオン抵抗を約50%低減できることを実証した。

IGBTの耐圧は維持、ゲート電圧は5Vに低下

東京工業大学科学技術創成研究院未来産業技術研究所の筒井一生教授らは2016年12月、微細加工技術により、シリコンパワートランジスタの性能を向上させることに成功したと発表した。従来に比べオン抵抗を約50%低減できることを実証した。

パワートランジスタ市場では、価格などの面からシリコンIGBT(Si Insulated Gate Bipolar Transistor)が占める比率は依然として高い。ところが、性能面ではオン抵抗の低減による低損失化などが課題となっている。今回は、微細化(スケーリング)による高性能化に注目し、3分の1スケーリングのSi-IGBTを作製して、その効果を実証した。

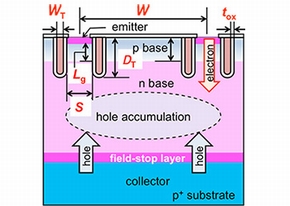

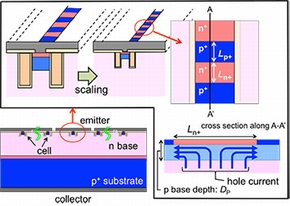

研究チームは、現行のSi-IGBTと同等寸法のデバイスと、新規スケーリングの概念を用いて微細化した新構造のデバイスを作製し、その特性を比較した。作製したSi-IGBTの構造や電流をオン/オフする動作については、従来のデバイスと変わらないという。

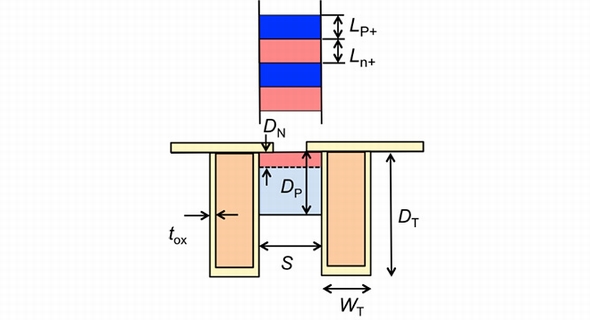

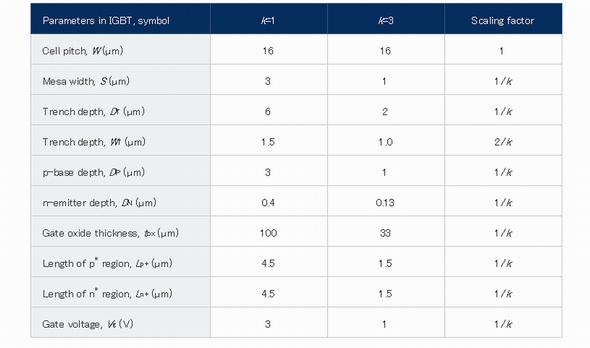

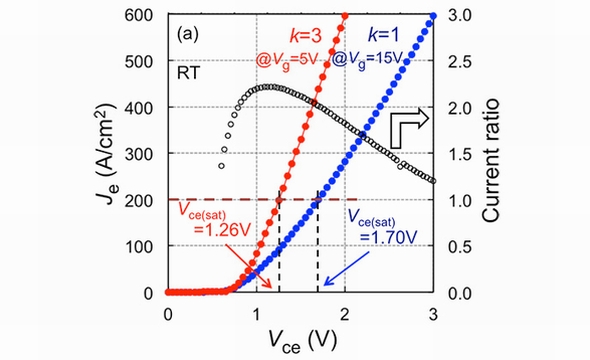

デバイス作製に当たり、寸法の微細化比率をスケーリングファクター1/kで表した。従来デバイスはk=1で、新規デバイスはk=3となる。断面構造において、トレンチゲート周りの寸法は1/kに比例縮小したが、隣接するトレンチゲートまでの距離(W)は一定とした。IGBTの2次元のスケーリングは、CMOS構造のデバイスと異なり、縦横スケーリングが逆の影響、効果になることもあるという。その効果は複雑で、これまでのシミュレーション結果によれば、単位面積当たりのオン電流の密度は増大することが予測されている。今回は、試作したデバイスでこの予測を実証した。

研究グループは、スケーリングで予測されるラッチアップ耐性の劣化に対する対策も行った。試作時にスケーリングパラメーターの一部を見直している。さらに、デバイスの奥行き方向に交互に作られる表面のp形領域とn形領域のピッチ(Lp+およびLn+)も1/kに縮小した。

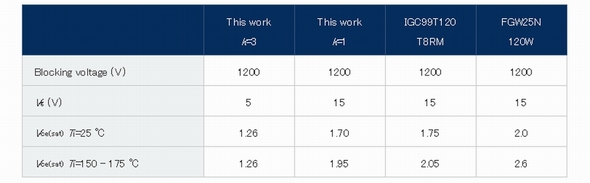

エミッター−コレクター間飽和電圧と呼ぶ、特定のオン電流密度(飽和電流密度)における電圧を測定したところ、k=3スケーリングで1.26Vとなった。従来(k=1)の1.7Vに比べると約70%である。同じエミッター−コレクター間電圧における電流はスケーリングにより約2倍となった。このことは、オン抵抗が半減したことを示す。これらの結果から、スケーリングによりIGBTの低損失と高効率化を実現できることが分かった。

また、IGBTのゲート電圧も従来の15Vに対し、スケーリングによって5Vまで低減させることができた。これによって、IGBTを駆動する回路の消費電力を低減することができ、システムレベルでの高性能化と低コスト化を可能とした。

今回のスケーリングは、IGBTのゲート周りに対して行ったもので、トランジスタ耐圧に関わるnベース層の厚みは変更していない。このため、新構造のIGBTでも耐圧1000〜数千Vは維持されるという。

今回の成果は、2016年12月6日に米サンフランシスコで開かれた国際会議「IEDM2016(International Electron Devices Meeting)」で、東工大、東大、九州工業大学、明治大学、産業技術総合研究所、東芝、三菱電機の共同研究として発表された。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

情報漏えいの危険がない、分散ストレージを開発

情報漏えいの危険がない、分散ストレージを開発

情報通信研究機構(NICT)は東京工業大学と共同で、分散ストレージシステムにおいて認証、伝送、保存というすべての工程で情報理論的安全性を担保するシステムの実証実験に成功した。計算機の処理能力が飛躍的に向上しても情報漏えいの危険を回避できる技術だという。 蓄電池内部の挙動、原子レベルで解析に成功

蓄電池内部の挙動、原子レベルで解析に成功

東京工業大学らによる研究グループは、蓄電池内部における充放電時の挙動を、原子レベルで解析することに成功した。中性子線を用いて非破壊かつリアルタイムに観測できるシステムを開発したことによって実現した。 希少元素を使わない赤く光る窒化物半導体を発見

希少元素を使わない赤く光る窒化物半導体を発見

東京工業大学と京都大学の共同研究チームは2016年6月、希少元素を使わずに、赤色発光デバイスや太陽電池に応用できる新たな窒化物半導体を発見、合成したと発表した。 高周波圧電共振器の課題を解決する回路

高周波圧電共振器の課題を解決する回路

東京工業大学と情報通信研究機構(NICT)は2016年6月15日、シリコン上に集積できる高周波圧電共振器による位相同期回路(PLL)を、無線モジュールの水晶発振器を置き換え可能な性能で実現する技術を開発したと発表した。 低閾値電圧の有機Trを実現する化合物を安定合成

低閾値電圧の有機Trを実現する化合物を安定合成

東京工業大学は2016年5月、閾(しきい)値電圧の低い有機トランジスタ(Tr)として機能する化合物を安定的に合成する手法を開発した。 40GHz帯/60GHz帯協調による無線網の実証に成功

40GHz帯/60GHz帯協調による無線網の実証に成功

ソニーやKDDI研究所などは2016年2月29日、40GHz帯と60GHz帯を協調させた次世代高速ワイヤレスアクセスネットワーク構築し、実証に成功したと発表した。