2.5Dパッケージング技術を適用したFPGA:ISSCC 2017でIntelが発表

現在、米国で行われている国際学会「ISSCC 2017」で、Intelが、2.5Dパッケージング技術を使ったFPGAについて論文を発表した。

Intelのパッケージング技術とAMDの「Zen」

Intelが、2017年2月5〜9日に米国カリフォルニア州サンフランシスコで開催されている「ISSCC 2017」において、同社の次世代FPGA「Stratix X」に関する論文を発表し、2.5D(2.5次元)パッケージングを置き換える低コストの代替技術について詳細を明らかにした。

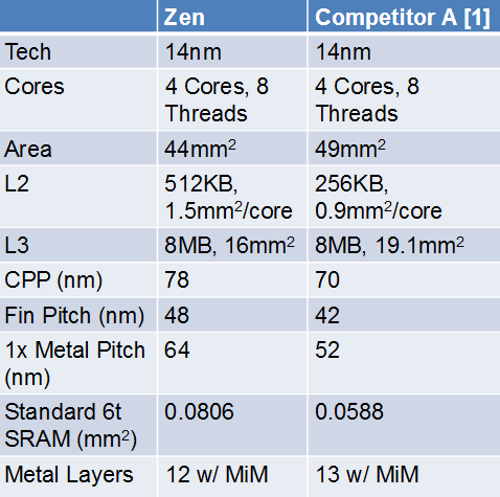

また、AMDは、同じセッションの中で、同社のx86プロセッサ「Zen」を披露した。14nmプロセスを適用したIntelの最新CPUと比べて、ダイサイズを10%縮小することに成功したという。

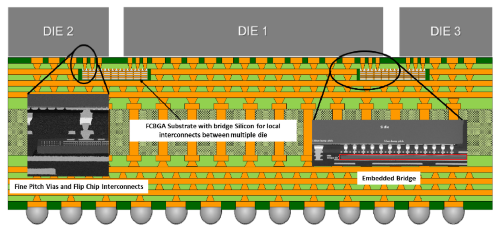

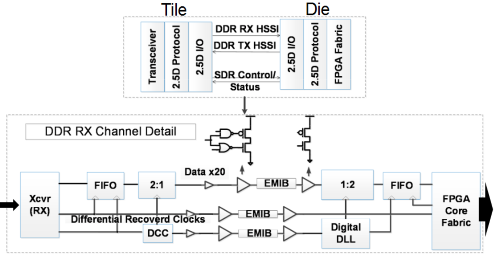

Stratix Xは、Intel独自のEMIB(Embedded Multi-die Interconnect Bridge)技術を使って、FPGAを4つのトランシーバーと接続している。シリコンダイで作成したブリッジをBGA基板に搭載したことで、TSMCが開発した「CoWoS(Chip on Wafer on Substrate)プロセス」で使われているシリコン基板に比べて大幅な小型化に成功したという。CoWoSプロセスは、IntelのライバルであるFPGAベンダーXilinxやGPUベンダーNVIDIAにも採用されている。

EMIB技術は、55μmのマイクロバンプと、100μm以上のフリップチップバンプを組み合わせて使用することにより、それぞれ96個のI/Oを搭載したトランシーバーチャンネルを、最大で24個サポートすることができるという。専用プロトコルを使用し、1ダイ当たり1.2pJ/ビットで、1ピン当たり2Gビット/秒を実現することができる。

このブリッジは現在、4つの28GHz SerDes(Serializer/Deserializer)をFPGAに接続している。IntelのエンジニアであるDavid Greenhill氏は、ISSCC 2017において論文を発表し、「Intelは、SerDesと各種外部チップの高速化実現に向けたロードマップを用意している」と述べている。

セッションには多くの聴衆が集まり、今回のパッケージング技術に関する質問もいくつか上がった。Greenhill氏は、Xilinxのエンジニアが提示した質問に対し、「Intelの開発チームは、56G SerDesへの移行を実現する上で、温度関連の課題についても問題なく対処できると考えている」と答えた。

Intelは2014年9月に、ファウンドリーサービスの一環としてEMIB技術を発表したが、今のところまだ、EMIBの新規ユーザーを発表するには至っていない。14nmプロセス適用のStratix Xは、ギガヘルツ動作の560mm2のファブリック上に、280万個のロジックエレメントを搭載するという。

AMDは、別の論文の中で、「同社が間もなく発表を予定しているZENコアは、Intelが現在出荷している第2世代の14nmプロセッサと比べて、ダイサイズを10%縮小できる見込みだ」としている。セッションに参加したアナリストやIntelのエンジニアも、「Zenコアは、非常に高い競争力を持っている。しかし、AMDにとって、ダイサイズの縮小を実現したことが低コスト化の実現につながるかどうかは、現在まだ明らかになっていない数々の変動要素によって決まることになるだろう」と述べている。

論文によると、AMDが今回採用した技術は、既存のチップと比べてスイッチング容量を15%低減することが可能だという。例えばZenは、AMDにとって初となるMIM(metal-insulator-metal)構造のキャパシターを使用したことにより、動作電圧の低減や、1コア当たりの供給電圧の増加、周波数の制御機能の向上などを実現することができたという。

同社のエンジニアたちは、スイッチング容量を低減すべく、ここ1年以上にわたり、高活動領域の電力ベンチマークを週1回のペースで追跡してきた。現在は、3.4GHzで同時マルチスレッディング動作を実行する8コアの設計を2種類、開発したという。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

自動運転でFPGAの期待値高まる、ザイリンクスがデモ

自動運転でFPGAの期待値高まる、ザイリンクスがデモ

ザイリンクスは、「第9回 国際カーエレクトロニクス技術展」(2017年1月18〜20日、東京ビッグサイト)で、ディープラーニングを使った歩行者認識、IRカメラによるドライバーモニタリングシステム、Ethernet AVBを使った高速伝送のカメラシステムなど、ADAS(先進運転支援システム)や自動運転向け技術をデモ展示した。 CMOSイメージセンサーにDRAMを積層

CMOSイメージセンサーにDRAMを積層

ソニーは、DRAMを積層した3層構造の積層型CMOSイメージセンサーを開発した。高速読み出しを実現したことで、スマートフォンでもスーパースローモーション動画の撮影などが可能となる。 EVモーター制御の専用回路を開発、CPU負荷軽減

EVモーター制御の専用回路を開発、CPU負荷軽減

ルネサス エレクトロニクスは、車載用マイコン向けのモーター制御専用回路技術「IMTS(Intelligent Motor Timer System)」を開発した。フィールド指向制御演算の処理を高速で実行し、CPUの負荷も大幅に軽減することができる。 Intel、10nmプロセスでは新技術は導入せず

Intel、10nmプロセスでは新技術は導入せず

Intelは「ISSCC 2016」でムーアの法則の維持と“ポストCMOS”について講演し、10nmプロセスでは新しい技術は導入しないことを断言した。 Intel、IoTを巡ってARMと対決

Intel、IoTを巡ってARMと対決

Intelがこのほど、自動車、産業機器市場向けのリアルタイム性能を備えた新SoCを発表したことで、ARMとのIoT(モノのインターネット)の市場を巡る戦いが激化しつつある。 研究開発コミュニティーが置かれた危うい状況

研究開発コミュニティーが置かれた危うい状況

研究開発コミュニティーは「常に」危機に曝されてきた。研究開発に関わるエンジニアであれば、「研究不正」「偽論文誌・偽学会」「疑似科学」といった、研究開発コミュニティーを取り巻くダークサイドを知っておくにこしたことはない。本連載では、こうしたダークサイドを紹介するとともに、その背景にあるものを検討していく。