近接場結合を用いた3D集積、電力効率の1桁改善を:慶応大の黒田忠広氏が語る(2/2 ページ)

電力効率の改善なくして、性能改善なし。 慶応義塾大学の理工学部電子工学科で教授を務める黒田忠広氏は、講演内でこう語る。電力効率の改善には新しいトランジスタ構造などの導入が検討されているが、黒田氏が提案するのは「近接場結合」による3D集積技術である。

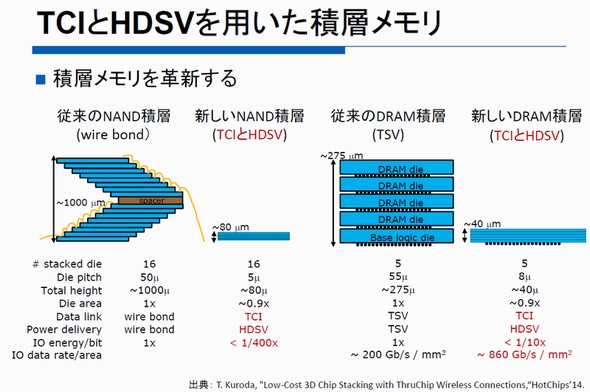

積層メモリを革新するTCIとHDSV

黒田氏が電力効率の改善へ提案するのは、チップやモジュールの接続をTSVやコネクターなどの機械式から、電子式の「近接場結合」による3D集積へと変えることだ。「Suica」など電子マネーに用いられている近接場は、移動通信などに用いられる遠方場と比較して、少し距離が離れると急激にエネルギーが減衰するため通信距離が短い。しかし、あまり飛ばないために混信せず、見えない配線があるかのように対象へ届く特長を持つ。

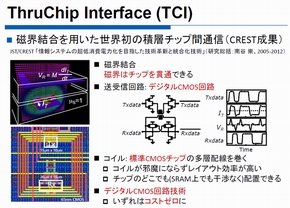

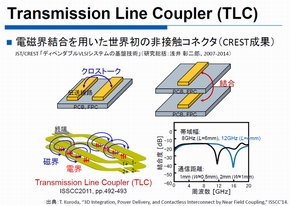

黒田氏らの研究グループは、科学技術振興機構(JST)の戦略的創造研究推進事業(CREST)の助成を受けて、近接場結合を用いた集積技術の開発を行ってきた。それが「TCI:ThruChip Interface」と「TLC:Transmission Line Coupler」となる。

TCIは、磁界結合を用いた積層チップ間通信である。黒田氏は「磁界は、配線や基板があったとしても、チップの中をきれいにすり抜ける」と語る。TCIはウエハー工程の中で、標準CMOSチップの多層配線を巻くだけのため、追加のプロセスが必要なTSV(シリコン貫通ビア)と比べてコストメリットが高い。設置場所にも制約がなく、転送速度もTSVの2倍以上とする512Gバイト/秒、通信電力も低いとメリットを強調する。

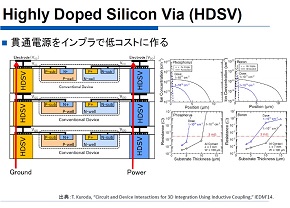

黒田氏は「電源はどうするのかと聞かれるが、貫通電源をインプラで低コストに作る『HDSV:Highly Doped Silicon Via』の実現性を検証している」と語る。公式Webサイトによると、HDSVでは高濃度で深い不純物ウェルを用いて積層チップに給電する。シリコン基板を十分に薄くすると、不純物ウェルが高濃度のまま裏面に到達するため、裏面側のチップとオーミック接合ができるという。「TCIとHDSVを組み合わせることで、メモリが容易に積層可能となり、電力の大幅な削減が期待できる」(黒田氏)

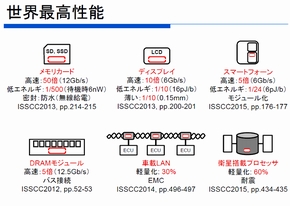

従来の製造方法による積層メモリと、「TCI」と「HDSV」を用いた積層メモリの性能比較。大幅に薄型化できるだけでなく、NAND型フラッシュメモリの場合は1ビット当たりのI/Oエネルギーは400分の1以下、DRAMの場合は10分の1以下と大幅な電力削減が期待できるという (クリックで拡大) 提供:黒田忠広氏

電力効率の1桁改善を目指す

TLCとは、電磁界結合を用いた非接触のコネクターとなる。隣接した並行する信号の影響で発生するクロストークノイズを活用することで、非接触のコネクターを実現。伝送速度は、最大12Gビット/秒を超えるという。通信距離の増加や、インピーダンスの整合が取れるため広帯域であるといった特長を持つ。非接触にしたことで、防水や防じんなどの耐性も強くなり、「ディペンダビリティを損なわない」と黒田氏は語る。

黒田氏は、最後に「電力効率の改善なくして、性能の改善はない。そのためには、低電圧化と低容量化が求められる。最先端の研究では、低リークなデバイスとディペンダブルな回路システムで0.3Vを目指している。加えて、今回紹介したTCIとTLCを用いたチップとモジュールの3D集積により、電力効率の1桁改善を目指す」とまとめた。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ムーアの法則の“新たな意味”とは

ムーアの法則の“新たな意味”とは

台湾半導体産業協会の専門家は、今後ムーアの法則は、「半導体の集積率の向上」というよりも、より実質的な意味を持つようになると指摘する。3次元構造やTSMCの「InFO」のようなパッケージング技術によって性能の向上を図っていくというものである。 ISS 2017で語られた半導体技術の今後(前編)

ISS 2017で語られた半導体技術の今後(前編)

米国で開催された「Industry Strategy Symposium(ISS)」(2017年1月8〜11日)では、半導体技術の今後に関する議論が幾つか展開された。ナノワイヤトランジスタやGAA(Gate All Around)トランジスタといった次世代トランジスタ技術や、増加の一途をたどる設計コストなどについて、専門家たちが見解を披露している。 Intel、アリゾナのFab 42に70億ドルを投資へ

Intel、アリゾナのFab 42に70億ドルを投資へ

Intelが、アリゾナ州に保有する製造工場「Fab 42」に70億米ドルを投資する予定であることを明らかにした。Intelは2014年1月に、Fab 42の稼働を延期することを発表したが、7nmプロセスの実現に向け、EUV(極端紫外線)露光装置の導入なども検討しつつ、同工場への投資を進めるとみられる。 GFが中国に工場建設、痛手を負うのは?

GFが中国に工場建設、痛手を負うのは?

GLOBALFOUNDRIES(GF)が中国の成都に工場を建設する。巨額の資金を投じて半導体産業の強化を進める中国にとって、これは朗報だろう。では、痛手を被る可能性があるのは誰なのか。 TSMC、3nmチップの工場建設計画を発表

TSMC、3nmチップの工場建設計画を発表

TSMCが5nmおよび3nmチップの製造工場を新たに建設する計画を発表した。大手ファウンドリー各社のプロセス開発競争は激化の一途をたどっている。 進む7nmプロセスの開発、TSMCとIBMが成果を発表

進む7nmプロセスの開発、TSMCとIBMが成果を発表

米サンフランシスコで開催された「IEDM 2016」では、TSMCとIBMがそれぞれ最新プロセス技術について発表し、会場を大いに沸かせたようだ。