ムーアの法則、半導体業界はどう捉えるべきか(前編):技術開発の指針の役割は終えた?(2/2 ページ)

台湾Etron TechnologyのCEOであるNicky Lu氏は、「ムーアの法則」は、技術開発の方針としての役目を既に終え、ビジネス的な意味合いの方が強くなっていると述べる。半導体メーカーが今、ムーアの法則について認識すべきこととは何なのか。

Silicon 2.0、Silicon 3.0時代

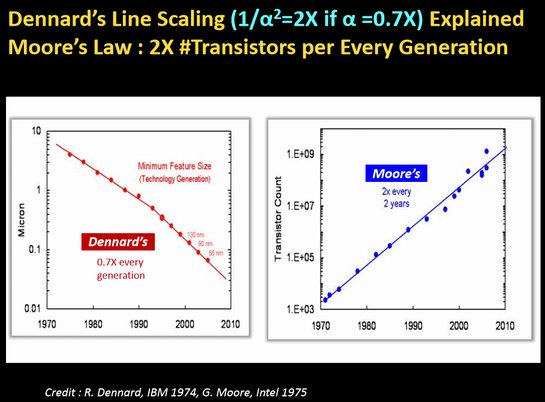

Lu氏はもともと、IBM Research Divisionにおいて研究キャリアをスタートさせ、1974年に「スケーリング則」を提案したR.H. Dennard(ロバート・デナード)氏と、密接に仕事をしてきたという。Lu氏は、2016年11月7日に富山県で開催された「A-SSCC 2016(IEEE Asian Solid-State Circuits Conference)」において、「A New Silicon Way」と題する論文を発表している。

同氏はこの論文の中で、半導体業界が現在、ムーアの法則を実際にどのように位置付けているのか、そしてこの先に何が起こり得るのかについて、説明している(関連記事:ムーアの法則の“新たな意味”とは)。

Dennard氏は、1974年に発表した共同執筆論文の中で、「トランジスタサイズが縮小するにつれて、1ノード当たりの電力密度は1世代ごとに、集積回路全体の消費電力量を大幅に増加させることなく向上していく。しかし、このような現象は最終的に、2005〜2007年に限界に達するだろう」と述べている。一般的なプレーナ型トランジスタのピッチを、1世代ごとに0.7倍に微細化するという、Dennard氏のスケーリング則の基礎を構築する法則の実現に執着してきた結果、現在ではリーク電流の増加という難題に直面するようになった。リーク電流が増加すると、特に28nm以降のプロセス技術では、半導体チップが過熱してしまうのである。

Lu氏は、「Dennard氏のスケーリング則と同様に、ムーアの法則もその当時、事実上の終えんを迎えていたはずだった」と主張する。

「ムーアの法則は28nmプロセスで終えんを迎える」という主張は、決して新しい見解ではない。例えば、MonolithIC 3Dの創設者であるZvi Or-Back氏は以前から、「半導体業界は、28nmプロセス以降も引き続き、トランジスタの小型化を実現することはできるが、コストが増大していくことになる。このためムーアの法則は、28nmプロセスを最後として終わりを迎えることになるだろう」と主張してきた。

一方Lu氏は、「ムーアの法則は、形骸化しながらも継続していくとみられる」と述べている。

Lu氏の見解によると、ムーアの法則がこれまで存続してきたのは、Intelがトライゲート構造のトランジスタを開発したためだという。Intelの開発チームは、22nmプロセス技術への移行時に、フィン構造のトランジスタ、いわゆるFinFETを開発し、ゲート面積の拡張に成功したのだ。

Lu氏は、FinFET登場以降の時代を、「Silicon 2.0」と呼ぶ。Silicon 2.0時代の半導体メーカーは、既存のプレーナ型トランジスタを、新しいトライゲート構造のトランジスタに置き換えていく。

メモリチップメーカー各社も単位面積の微細化に着手し、東芝が48層の3D(3次元) NAND型フラッシュメモリを開発した他、Samsungも64層の3D NANDフラッシュを開発している。Lu氏は、「半導体メーカーは、3Dを実現することにより、適用技術は32nmプロセス程度でありながら、実質的には13nmプロセスに相当する技術を達成したのだ」と説明する。

Silicon 2.0は、3Dトランジスタと3Dセル構造のいずれかによって実現された時代だといえる。

Silicon 2.0時代には、22/20nmから7nmへと技術ノードが進んだが、SiP(System in Package)やMCM(マルチチップモジュール)、3D積層などの新しい技術の開発も進んだ。Lu氏はこれを、「容量面での微細化」として「Silicon 3.0」と呼んでいる。

Silicon 3.0時代は、異種統合というコンセプトにより、特にさまざまな技術を適用して半導体チップを積層するという点で、前途有望だといえる。Silicon 3.0時代には、シリコン材料とノンシリコン材料とを純粋に統合し、シリコンを中心としたナノシステムの構築の実現が進むかもしれない。

(後編に続く)

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

東芝問題は日本の製造業に共通し得る課題なのか

東芝問題は日本の製造業に共通し得る課題なのか

米国の原子力子会社の巨額損失により債務超過に陥るなど経営危機を迎えている東芝。経営危機に陥った理由を分析していくと、東芝固有の問題だけではなく、他の日系電機メーカーにも起こり得る共通の課題が見えてくるのだった。 TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

今回から前後編に分けて「CoWoS(Chip on Wafer on Substrate)」を解説する。CoWoSの最大の特長はシリコンインターポーザを導入したことだが、では、なぜシリコンインターポーザが優れているのだろうか。シリコンインターポーザに至るまでの課題と併せて説明する。 ムーアの法則、50年をたどる

ムーアの法則、50年をたどる

1965年、IntelのGordon Moore(ゴードン・ムーア)氏が雑誌に掲載したトランジスタに関する予見は、「ムーアの法則」として半導体技術の発展の大きな原動力となった。ムーアの法則によってトランジスタがどれほど進化してきたのか。50年を振り返ってみる。 Intel方針転換の真意を探る

Intel方針転換の真意を探る

2016年、Intelはモバイル事業からの撤退を決めるなど方針転換を行った。そうした方針転換の真の狙いを、Thunderbolt用チップ、そして、7年前のTSMCとの戦略的提携から読み取ってみたい。 「iPhone 7 Plus」を分解

「iPhone 7 Plus」を分解

2016年9月16日に発売されたApple(アップル)のスマートフォン「iPhone 7 Plus」を、iFixitが分解した。 Nintendo Switchのチップ解剖から考えるデグレード版Tegra X1を選んだ理由

Nintendo Switchのチップ解剖から考えるデグレード版Tegra X1を選んだ理由

今回は、任天堂の歴代ゲーム機の搭載チップを簡単に振り返りつつ、2017年3月発売の新型ゲーム機「Nintendo Switch」の搭載チップについて考察する。発売前「カスタマイズされたTegraプロセッサ」とアナウンスされたプロセッサの内部は、意外にも「Tegra X1」の“デグレート版”だった……。