シノプシス、性能重視の新ARCプロセッサを発表:ハイエンド組み込み機器向け

シノプシスが、組み込みアプリケーション向けプロセッサの新ファミリー「DesignWare ARC HS4x」「DesignWare ARC HS4xD」を発表した。処理性能を重視したファミリーだが、シノプシスは、プロセッサの製品戦略としては「性能の向上ばかりを重視するわけではなく、組み込み機器に求められている機能をきちんと備えているかの方が重要」だと強調した。

性能を重視したARCプロセッサの新ファミリー

シノプシスは2017年5月23日(米国時間)、組み込み機器向けの32ビットRISCプロセッサ「DesignWare ARC HS4x」「DesignWare ARC HS4xD」(以下、HS4x)を発表した。「DesignWare」はシノプシスが手掛けるIP(Intellectual Property)製品のブランド名だ。今回発表した新製品は、CPUコアのIPになる。

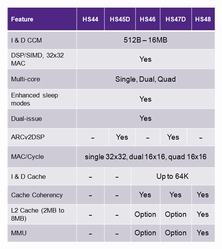

新ファミリーには、「HS44/HS46/HS48/HS45D/HS47D」の5つがある。それぞれシングル、デュアル、クアッドコアの構成が可能で、1コア当たり6000DMIPSの命令実行ができるDual-issueスーパースカラーのアーキテクチャを搭載している。ARCプロセッサとして、同アーキテクチャを搭載するのは初めてとなる。これにより、前世代品の「DesignWare ARC HS3x」ファミリーに比べてRISC性能が25%向上した。

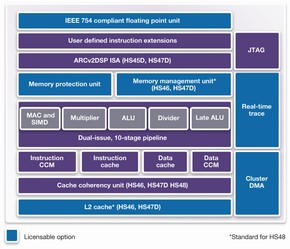

HS44/HS46/HS48の3つは、「ARCv2 インストラクション・セット・アーキテクチャ(ISA)」に基づいて開発されたもので、消費電力とシリコン面積を抑えられることが特長だ。16nm FinFETプロセスを適用した場合、シリコン面積はわずか0.06mm2で、消費電力は37mW/MHzとなっている。HS46とHS48は、最大64KBの命令キャッシュとデータキャッシュとフルL1キャッシュ・コヒーレンシをサポートするMMU(メモリ管理ユニット)を搭載。HS48は、最大8MBのL2キャッシュと、対称型マルチプロセッシング(SMP)LinuxをサポートできるMMUも搭載している。

HS45DとHS47Dは、HS4xと同等の制御機能に加えて、ベースバンド、オーディオ、音声、その他信号処理アプリケーションに向けたDSP機能を提供する。整数除算器、64ビット乗算命令、ベクター加算および減算、IEEE 754準拠の浮動小数点ユニットを実装するといったオプションを使って、演算スピードを向上できる。

「性能だけで競争しない」

HS4xとHS4xDは、ワイヤレスベースバンド、ホームネットワーク、車載制御およびインフォテインメントシステム、産業機器、ホームオートメーション、SSDといった幅広い組み込みアプリケーションに向ける。シノプシスのARC Processors & Subsystems Solutions Groupでプロダクトマーケティングのシニアマネジャーを務めるMichael Thompson氏は、「われわれは、スマートフォンやサーバなどの分野は狙わない。ターゲット市場はあくまでも組み込み機器だ。そのため、処理性能だけで競合他社と競争しようとは思っていない。それよりも、高性能な組み込み機器を実現するために必要な機能を備えていることの方が重要だ。HS4xとHS4xDは性能を重視したファミリーだが、それは、われわれが対象としてきた組み込み機器で求められる処理性能が、格段に上がってきたからだ」と強調した。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

シーメンスのメンター買収、EDA業界への影響は

シーメンスのメンター買収、EDA業界への影響は

2016年11月、Siemens(シーメンス)によるMentor Graphics(メンター・グラフィックス)の買収が発表され、業界に衝撃が走った。この買収は、実際のところ設計ツール業界、とりわけEDA業界にどのような影響を与えるのだろうか。Siemens PLM SoftwareとMentorのキーパーソンに直接、その疑問をぶつけてみた。 ARMの新型コア「Cortex-A75/A55」、AIを促進

ARMの新型コア「Cortex-A75/A55」、AIを促進

「COMPUTEX TAIPEI 2017」開催前日の記者説明会で、ARMが新型CPUコア「Cortex-A75」と「Cortex-A55」を発表した。最大8種類の異なるCPUコアを1クラスタ上に構成できるアーキテクチャ「DynamIQ」をベースにした、最初のCPUコアとなる。新Cortex-Aシリーズの最大のターゲット市場は、AI(人工知能)だ。 ムーアの法則は健在! 10nmに突入したGalaxy搭載プロセッサの変遷

ムーアの法則は健在! 10nmに突入したGalaxy搭載プロセッサの変遷

今回はSamsung Electronicsの最新スマートフォン「Galaxy S8+」に搭載されているプロセッサ「Exynos8895」を中心に、Galaxy Sシリーズ搭載プロセッサの進化の変遷を見ていく。そこには、ムーアの法則の健在ぶりが垣間見えた。 Samsung、2020年に4nmのリスク生産を開始

Samsung、2020年に4nmのリスク生産を開始

Samsung Electronicsは、ファウンドリー技術のロードマップを発表した。2020年に4nmプロセスを用いて、同社独自の「MBCFET(Multi Bridge Channel FET)」のリスク生産を開始する予定だという。 Googleが第2世代TPUを発表、処理性能は180TFLOPS

Googleが第2世代TPUを発表、処理性能は180TFLOPS

Googleは、機械学習(マシンラーニング)向けのプロセッサ「TPU(Tensor Processing Unit)」の第2世代を発表した。トレーニングと推論の両方に最適化されたもので、処理性能は180TFLOPSになるという。 ARMがもたらした“老舗コンサバ、新興アグレッシブ”の現状

ARMがもたらした“老舗コンサバ、新興アグレッシブ”の現状

ARMコアを使うことで、中国半導体メーカーも最新のCPUコアを用いたチップが作れるようになった。それは同時に、中国において、「老舗のメーカーは守りに入り、新興のメーカーに攻めに出る」という状況をもたらしている。