EUVの量産適用、半導体業界は前向きな見方:数年前から大きく変化

業界団体eBeam Initiativeの調査によると、EUV(極端紫外線)リソグラフィの実用化に対する業界の見方は、だいぶ前向きになっているようだ。

「EUVは導入されない」とする回答者は1%

業界団体eBeam Initiativeは2017年9月11日(米国時間)、同年夏に実施した調査の結果を発表した。それによると、半導体チップメーカーの経営幹部たちは、「半導体業界は今後、EUV(極端紫外線)リソグラフィとマルチビームマスクライターを導入する方向に進んでいく」とする、楽観的な見方を強めていることが明らかになった。現在、最先端デバイスの製造は、複雑化と高コスト化の一途にあるが、新たなシステムの導入により、さらなる技術進展を実現できると期待されている。

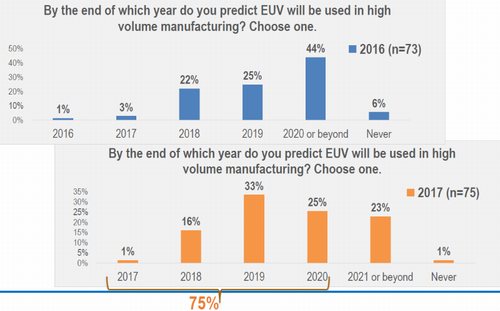

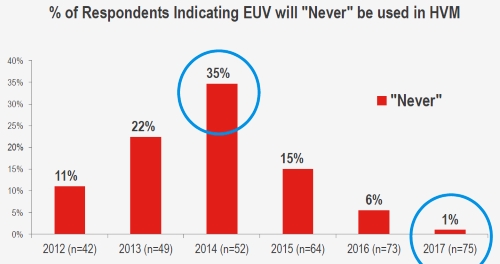

半導体業界の指導者たち75人を対象とした調査の結果によると、「EUVは2021年までに、量産に適用されるようになる」とする回答の割合が、全体の75%に達したという。また、「EUVが導入されることは絶対にない」とする回答は、2014年当時の調査では35%と高く、2016年には6%だったが、今回はわずか1%にまで減少した。

業界のベテランで、業界団体eBeam Initiativeの広報担当者を務めるAki Fujimura氏は、「EUVは今後数年以内に、7nmプロセスを皮切りに、確実に導入されていく見込みだ」と述べている。

IntelとSamsung Electronics、TSMCはこれまで、EUVリソグラフィ装置メーカーであるASMLに、数十億米ドル規模の投資を行ってきた。ASMLは2013年に、リソグラフィ光源技術を手掛けるCymerを買収し、複雑かつ高コストの技術の推進に取り組んできた。Fujimura氏は、「ここ数年の間に、7nmおよび5nmプロセスの開発状況がひどく悪化したため、ついに誰もが、『この開発がうまくいかなければ、業界全体が苦境に陥ることになるだろう』と声を上げるようになった」と述べる。同氏は現在、マスク欠陥の修正を加速するためにGPUを使用したシステムの開発を手掛けるメーカーD2Sにおいて、チーフエグゼクティブを務めている。

EUVへの移行は、決して簡単ではない。半導体メーカーは、まず既存の液浸ステッパーを使用して7nmプロセスを適用してから、一部のステップをEUVに移行させることにより、マルチパターニングの必要性を排除していく考えのようだ。

Fujimura氏は、「これまでにない新技術であるEUVは、それをサポートするための装置やエコシステムに多額の投資を行う必要がある。EUVの導入は、徐々に進めなければならないため、直ちに最善の成果を求めることはできない」と指摘する。同氏にとってD2Sは、3社目の新興企業となる。それ以前は、1979年以降、Cadence Design SystemsをはじめEDA業界に身を置いてきた。

マスクメーカーが過去12カ月間に製造したEUVマスク数は1041枚で、その1年前の382枚と比べると大幅に増加している。トップ10社のマスクメーカーに対して行った別の調査結果によると、EUVマスクの歩留まりは、わずか64.3%にとどまっていたのに対し、過去12カ月間に露光した46万2792枚の全てのマスクでは、94.8%の歩留まりを達成したという。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(ASML編)

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(ASML編)

「SEMICON West 2016」で行われた次世代のリソグラフィ技術を展望するフォーラムから、各露光装置メーカーの講演内容を紹介してきた。今回は、半導体露光装置最大手であるASMLのEUV(極端紫外線)リソグラフィ開発状況を中心に紹介する。 EUVが実現間近か、250Wの光源を達成

EUVが実現間近か、250Wの光源を達成

ASMLが、「SEMICON West 2017」で、250WのEUV(極端紫外線)光源を用いたデモを披露した。EUVリソグラフィ用を商用化するには、250Wの光源が1つのマイルストーンとされているため、実際の量産ラインでの実用化は間近かもしれないという期待が膨らむ。 ASML、EUVリソグラフィ開発を加速

ASML、EUVリソグラフィ開発を加速

半導体リソグラフィ技術に関する国際会議「SPIE Advanced Lithography 2017」において、ASMLがEUV(極端紫外線)スキャナーを発表した。 EUVと液浸、FinFETとFD-SOI、GFの強みは2点張り

EUVと液浸、FinFETとFD-SOI、GFの強みは2点張り

2017年5月31日、来日したGLOBALFOUNDRIES(グローバルファウンドリーズ/GF)CMOSプラットフォーム事業部シニアバイスプレジデントのGregg Bartlett氏に7nm FinFET、12nm FD-SOIの開発状況などについてインタビューした。 3次元集積化(3D IC)の理想と現実

3次元集積化(3D IC)の理想と現実

今回は、なぜシステムを複数のチップに分ける必要があるのかを説明する。後半では、パッケージに求められる目標を達成する“究極のパッケージング技術”として期待されたシリコン貫通ビア(TSV: Through Silicon Via)と、旧世代のパッケージング技術との間に存在する、大きなギャップについて解説したい。 米半導体業界、ポスト・ムーアの技術を模索

米半導体業界、ポスト・ムーアの技術を模索

米国防高等研究計画局(DARPA)は、来たる「ムーアの法則」の終息に備え、“ポスト・ムーア時代”の技術の模索を本格化させている。材料、アーキテクチャ、設計の自動化の3つにターゲットを絞り、まずは2億米ドルを投資してプロジェクトを行う予定だ。