熱圧着プロセスを10分の1に短縮、新しい実装技術:日立化成が提案

日立化成は「SEMICON Japan 2017」(2017年12月13〜15日、東京ビッグサイト)で、TCB(Thermal Compression Bonding:熱圧着)プロセスにかかる時間を最大10分の1に短縮する実装技術を提案した。

TCBプロセスの時間を短縮

日立化成は、東京ビッグサイトで開催中の「SEMICON Japan 2017」(2017年12月13〜15日)で、TCB(Thermal Compression Bonding:熱圧着)プロセスにかかる時間を短縮する実装技術を提案した。

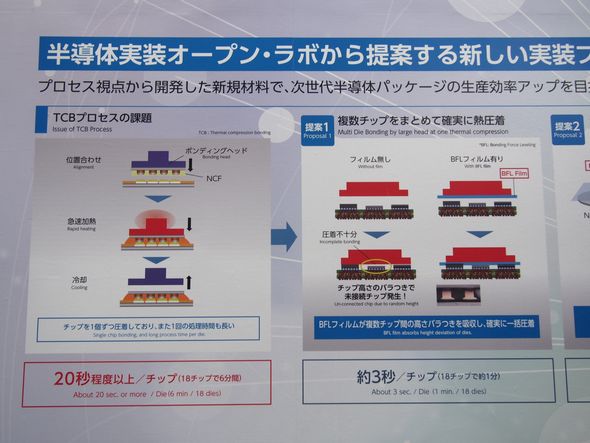

現状のTCBプロセスは、位置合わせ、熱圧着、冷却というステップで行われているが、チップを1個ずつ圧着している上に、処理時間が長いので、全体としてかなり時間がかかる工程になっている。日立化成によれば、処理時間の平均は1チップ当たり約20秒だという。

そこで日立化成は、まず複数のチップをまとめて熱圧着する方法を提案した。同社が開発した「BFL(Bonding Force Leveling)フィルム」を熱圧着ヘッドとチップの間に挟む。BFLフィルムは柔らかく、わずかに存在しているチップ高さのばらつきを吸収する。そのため、幾つかのチップを一気に圧着しても、高さのばらつきによってボンディングされていないチップが発生することがないという。この方法により、処理時間は1チップ当たり約3秒と、従来の方法に比べて6分の1以下になるとする。

2つ目の方法は、“熱圧着そのものをなくす”というものだ。こちらは、メモリチップをTSV(Through Silicon Via)で積層するような、3D(3次元)実装への適用を想定している。NCF(Non Conductive Film)をラミネートした上にチップを積層して仮搭載した後、一気にモールドして全体を形成し、その後のリフロー処理でチップ間のはんだ接続を行う。1つずつリフロー処理を行う必要はない。実装時間(仮搭載の処理)は1チップ当たり約2秒と、従来の10分の1になる。日立化成は、NFCとモールド樹脂を開発している。

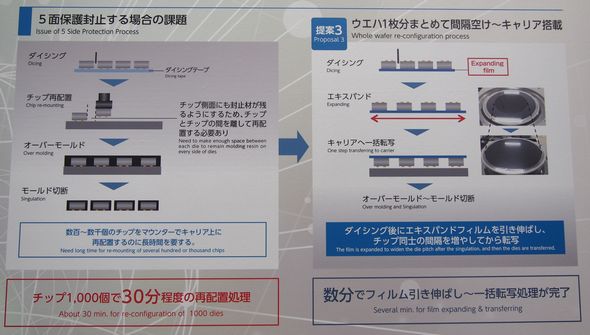

日立化成は、5面保護封止をする場合の新実装技術も展示した。従来は、ダイシングした後にチップを1つずつ再配置し、オーバーモールドを行い、切断する。最も時間がかかるのが再配置で、日立化成によれば、チップ1000個で約30分かかるという。そこで同社は、「ダイ・ギャップ・エクスパンディング・フィルム」を開発した。伸ばすことができる基板フィルムである。ダイシングした後にこのフィルムを引き伸ばすことで、チップとチップの間隔が広がるので、チップを再配置する必要がなくなる。あとは、間隔が空いたチップをフィルムごとひっくり返してキャリアに一括転写し、フィルムをはがしてオーバーモールドする。これにより、フィルムの引き伸ばしから転写処理まで、わずか数分で完了するという。

これらの実装技術はいずれも開発中で、日立化成は、実用化のメドについては明らかにしなかった。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

製造コスト「数十分の1」、卓上半導体工場

製造コスト「数十分の1」、卓上半導体工場

半導体製造の後工程に革新が生まれそうだ。コネクテックジャパンは製造プロセスを一新することで、後工程に必要なコストを抑え、実装時間を短縮するフリップチップ実装装置「MONSTER DTF」を開発した。特徴は低荷重、低温で半導体パッケージを基板に実装すること。例えばMEMSパッケージをフリップチップ実装できるようになり、最終製品の小型・軽量化にもつながるという。 GaN-MOSFET向けゲート絶縁膜プロセス、東芝が開発

GaN-MOSFET向けゲート絶縁膜プロセス、東芝が開発

東芝は、GaNパワーデバイス向けにゲート絶縁膜プロセス技術を開発したと発表した。「IEDM 2017」で発表したもの。しきい値電圧の変動を極限まで低減するという。 チップ部品の実装も可能なフィルム型コネクター

チップ部品の実装も可能なフィルム型コネクター

日本航空電子工業は、「プリンタブルエレクトロニクス 2017」(2017年2月15〜17日/東京ビッグサイト)で、チップ部品の実装が可能なフィルム型コネクターを展示した。 TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

今回から前後編に分けて「CoWoS(Chip on Wafer on Substrate)」を解説する。CoWoSの最大の特長はシリコンインターポーザを導入したことだが、では、なぜシリコンインターポーザが優れているのだろうか。シリコンインターポーザに至るまでの課題と併せて説明する。 パナソニック、低温硬化性の実装補強材を開発

パナソニック、低温硬化性の実装補強材を開発

パナソニックは、接合強度が要求される車載向け部品実装などの用途に向けて、低温硬化性の「二次実装アンダーフィル材」を開発、量産を始めた。 モノリシック3D IC、将来有望ながら課題は山積

モノリシック3D IC、将来有望ながら課題は山積

半導体チップの高速化や小型化を実現する技術として研究開発が続けられているモノリシック3D(3次元) ICだが、数多くの難しい課題が残っているようだ。