TSMCがロードマップを発表、EUV導入は19年前半:新パッケージング技術の開発も(2/2 ページ)

TSMCは、7nmプロセスの量産を開始し、さらにEUV(極端紫外線)リソグラフィを導入したバージョンの生産を2019年前半にも開始する計画も発表した。さらに、同社は5nmノードに関する計画も明らかにした。

300Wの光源を目指す

TSMCは2019年初めには、EUVを導入した量産を開始したい考えだ。2018年4月には、2〜3週間をかけて、250Wの光源による生産を持続するためのシステムを導入している。2019年には、量産に必要とされる300Wの達成を目指すという。

TSMCの技術開発部門で研究開発担当バイスプレジデントを務めるY.J. Mii氏は、「当社では今のところ、通常の電力レベルが145Wであるため、まだ実現への道のりは遠いといえる。しかし、スループットに関しては、生産に必要なレベルを達成できる見込みだ」と述べる。

また同氏は、「EUVは今後も、液浸ステッパーより優れたクリティカルディメンション均一性(CDU:Critical Dimension Uniformity)を実現することができるだろう」と述べ、いくつかの例を挙げた。TSMCは、N7+とN5の両方の複数層でEUVを適用する予定だとして、ASMLの「NXE3400」システムの導入を積極的に進めているという。

Samsung Electronicsは以前に、EUVによる生産を2018年に開始する予定だと発表していた。そのため、TSMCのEUV計画は、Samsungの生産開始予定から6カ月以内に始動することになる。Samsungは2018年5月後半に、イベントを開催する予定であることから、そのイベントでプロセス技術の進捗(しんちょく)について最新情報を明らかにするとみられる。

TSMCの5nmプロセス技術に関しては、EDAフローのバージョン0.5のリリースが2018年6月に、デザインキットのバージョン0.5のリリースが同年7月に、それぞれ予定されていることから、まだほんの初期段階にすぎない。PCIe Gen 4やDDR4、USB 3.1など、多くのIPブロックが実証されるのは、2019年以降になるとみられる。

TSMCは2019年末までに、10nmおよび7nmプロセス技術による生産量を3倍に拡大し、1年間当たり110万枚のウエハー生産量を達成したい考えだという。同社は現在、台湾で最も新しい工場となる「Fab 18」の建設を進めており、2020年には5nmプロセスによる製造を開始する予定だとしている。

パッケージング技術にも注力

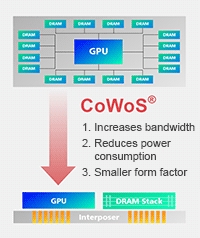

TSMCは、GPUをはじめとするプロセッサ向けの2.5次元(2.5D)のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」や、スマートフォンチップ向けのウエハーレベルのファンアウトパッケージング技術(FOWLP:Fan Out Wafer Level Packaging)「InFO」を採用した製品の拡充も進めている。

CoWoSチップは2019年初めごろに、シリコンインターポーザを選べるオプションが用意される見込みだ。さらに、2018年中には、バンプピッチが130μmのバージョンを実用化できる予定だという。

InFOの種類は現在、4種類ある。メモリ基板向けの「Info-MS」はSoC(System on Chip)とHBMを集積していて、2018年9月に実用化されるとみられている。「InFO-oS」は、DRAMに最適なバックサイドRDLピッチを搭載し、既に利用可能だという。マルチスタックオプション「MUST」は、1つまたは2つのチップを、インターポーザによって別の大型チップ上に集積する技術だ。「InFO-AIP(Antenna-in-Package)」では、フォームファクタが10%小型化し、ゲインが40%向上するという。5G対応ベースバンド向けフロントエンドモジュールなどをターゲットにしている。

パッケージング技術を専門とするTechSearch Internationalのプレジデントを務め、パッケージング分野のベテランアナリストであるJan Vardaman氏は、「InFOは、非常に重要なプラットフォームだ」と主張する。

「メモリをPoP(Package on Package)で集積した、ベースバンドチップやモデムチップ向けのInFOは、薄型化と小型化、高性能化を実現する優れた技術だ。『InFO on Substrate』についても、2μmのライン/スペースでさまざまなアプリケーションへの対応が可能になるため、今後普及が進んでいくだろう」(同氏)

TSMCは、これだけにとどまらず、新しいパッケージング技術を2種類発表している。

「Wafer-on-Wafer(WoW)」は、最大3つのダイを直接、接続することが可能だ。2018年4月30日の週に発表されたばかりの技術だが、ユーザーは、使用するEDAフローが、この接続技術に対応しているかどうかを確認する必要があるという。2018年6月には、EMIサポートを取得するとみられる。

2019年中にリリース予定の「SoICs(System-on-Integrated-Chips)」と呼ぶ技術の概要についても発表している。10μm未満のインターコネクトを使用して2つのダイを接続するとされるが、技術的な詳細については、まだ不明な点が多い。モバイルからHPCまでさまざまな用途に狙いを定め、異なるプロセス技術で製造されたダイを接続することが可能なため、SiP(System-in-Package)の一種ではないかとみられている。

【翻訳:青山麻由子、田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

今回から前後編に分けて「CoWoS(Chip on Wafer on Substrate)」を解説する。CoWoSの最大の特長はシリコンインターポーザを導入したことだが、では、なぜシリコンインターポーザが優れているのだろうか。シリコンインターポーザに至るまでの課題と併せて説明する。 Intel、10nmチップの量産開始を2019年に延期

Intel、10nmチップの量産開始を2019年に延期

Intelは、10nmチップの量産の開始時期を2018年後半から2019年に延期したことを明らかにした。歩留まりの改善の進展が見込みよりも遅いことが原因だという。 半導体プロセスの微細化は利益につながるのか

半導体プロセスの微細化は利益につながるのか

今後、半導体プロセスの微細化を進めていく上で、「微細化が本当に利益につながるのか」という疑問が出ているようだ。 ムーアの法則から離れることで、より自由に

ムーアの法則から離れることで、より自由に

半導体集積回路技術の国際会議「ISSCC 2018」が米国で始まった。初日の基調講演でAnalog Devices(ADI)のCEOは、「ムーアの法則から離れ、周りを見回すことで、本当に面白いことに向かって進んでいける」と語った。 シリコンが次の手、村田製作所のキャパシター戦略

シリコンが次の手、村田製作所のキャパシター戦略

2016年10月に村田製作所が買収したフランスのIPDiAは、シリコンキャパシターを事業として手掛けるほぼ唯一のメーカーだ。積層セラミックコンデンサーに比べてかなり高価なシリコンキャパシターは、その用途は限られている。それにもかかわらず、なぜ村田製作所はIPDiAの買収に至ったのか。 TSMCの1強時代に幕? “2ファブ・オペレーション”が可能になった14/16nm世代

TSMCの1強時代に幕? “2ファブ・オペレーション”が可能になった14/16nm世代

今回は昨今、発表が相次いでいる新しいGPUのチップ解剖から見えてくる微細プロセス、製造工場(ファブ)の事情を紹介する。チップ解剖したのはNVIDIAの新世代GPUアーキテクチャ「Pascal」ベースのGPUと、ゲーム機「PlayStation 4 Pro」にも搭載されているAMDのGPUだ。