日立、演算規模が可変なCMOSアニーリングマシンを開発:2018年8月よりサービス公開

日立製作所は2018年6月15日、解くべき問題に対応して演算規模をスケーラブルに構成できる世界最大規模のCMOSアニーリングマシンを開発し、同年8月よりパートナー向けにクラウドサービスとして公開すると発表した。

日立製作所は2018年6月15日、解くべき問題に対応して演算規模をスケーラブルに構成できる世界最大規模のCMOSアニーリングマシンを開発し、同年8月よりパートナー向けにクラウドサービスとして公開すると発表した。

従来技術のマシンでは、搭載するCMOSアニーリングチップを問題規模に応じて都度設計、開発する必要があり演算規模の拡張に制約があった。今回発表したマシンでは、複数のチップ同士を相互接続するネットワークを新たに採用したことで、演算規模をスケーラブルに拡張することができる。

世界最大規模となる10万2400パラメーターの問題に対応が可能

同社は、膨大な計算量が必要な「組合せ最適化問題」を実用的な時間内で処理することができるコンピュータの開発を進めており、CMOSアニーリングマシンはその一環として開発されている。

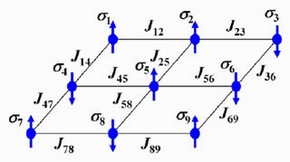

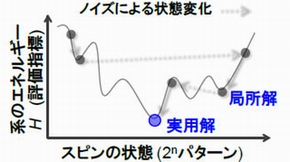

このマシンは、磁性体のスピンのふるまいを表現するモデルである「イジングモデル」の動作をCMOSで模擬し、解くべき問題をイジングモデルに変換することで演算を処理する。組合せ最適化の探索には、目的関数を熱ゆらぎによって確率的に遷移させ最適解を導出する「シミュレーテッドアニーリング」が用いており、これらをハードウェア的に実装することでCMOSアニーリングチップを開発した。

同社では2015年2月に、2万480パラメーターの問題に対応したCMOSアニーリングチップの試作を発表していた。このチップはASICに組み込まれており、イジングモデルのスピン個数や結合強さなどが可変ではないため、対応できる問題に限りがあった。これを受け2016年11月に、同社はFPGAによってCMOSアニーリングチップを開発したが、増加する問題規模に応じて都度チップ設計を行うことは期間やコスト面から困難であるため、スケーラブルに拡張できることが求められていた。

今回、同社はXilinx製UltraScaleファミリーのFPGAにCMOSアニーリングチップを実装し、チップ同士を相互に接続するネットワークを採用することで、解くべき問題規模に応じてチップ個数を拡張し、スケーラブルに構成可能なCMOSアニーリングマシンを開発した。

チップ間の接続では、高速に変化するパラメーターの値を隣接するチップに送受信する必要があるが、多数のチップを接続した場合にも通信量が急増しないことが求められる。同社は、チップのネットワーク構造にメッシュ型を採用し、全結合型と比較して省電力かつ低コストに大規模化することを可能とした。

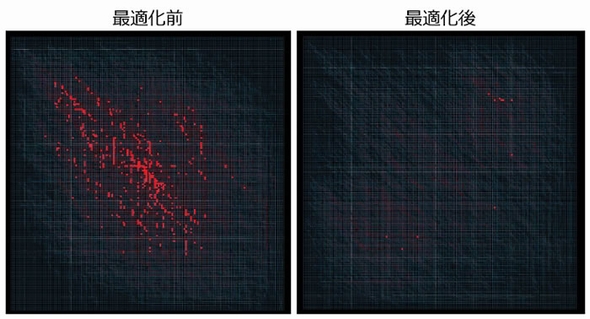

同技術により25個のチップを接続することで、10万2400パラメーターの問題に対応できる「世界最大規模」(同社調べ)のCMOSアニーリングマシンを開発。このマシンを用いて、都市交通の最短経路探索と混雑位置を避けるための車両経路制御のシミュレーションを行った。このマシンでは、従来マシンから25倍の面積に相当する約5km四方のエリアを扱うことができ、1台あたりの最短経路探索を数ミリ秒で処理したという。

約5km四方のエリアにおける都市交通最適化シミュレーションの実行例(クリックで拡大) 出典:日立製作所

縦横160本ずつの道路からなる道路網で2000台の車が交差点の端から端までランダムに移動するシミュレーションで、移動経路の最適化によって混雑箇所を示す赤い点が減少している

同社は、今回開発したCMOSアニーリングマシンを2018年8月より一般企業や大学、研究機関などのパートナー向けにクラウドサービスとして公開する予定だ。また、チップやマシン単体での提供は予定していないとするが、「アプリケーション開発やそれを支えるハードウェア技術の開発も含めて、最終的には2020年の実用化を目指す」(同社担当者)とした。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

量子コンピュータ並み!? 「組み合わせ最適化問題」を瞬時に解く新型コンピュータ

量子コンピュータ並み!? 「組み合わせ最適化問題」を瞬時に解く新型コンピュータ

日立製作所は、膨大なパターンから実用に適した解を導く「組み合わせ最適化問題」を、量子コンピュータ並みの性能で実現する新型コンピュータを試作した。室温での動作が可能で、従来コンピュータに比べると電力効率は約1800倍となる。 量子アニーリングの新シミュレーション法を開発

量子アニーリングの新シミュレーション法を開発

東北大学の大関真之准教授らは、量子アニーリングのシミュレーションを行うことができる新たな方法を開発した。最適化問題や機械学習に特化した量子計算技術の研究に弾みをつける。 光による量子コンピュータ、現行技術で実現へ

光による量子コンピュータ、現行技術で実現へ

北海道大学と京都大学の研究グループは、現在の技術レベルでも光による量子コンピュータを実現できる方法を開発した。量子ビットの誤り耐性を従来の100億倍に高めることで可能とした。 通常のシリコンで高性能「量子ビット」を実装

通常のシリコンで高性能「量子ビット」を実装

理化学研究所は2016年8月、産業で用いられる通常のシリコンを用いた半導体ナノデバイスで、量子計算に必要な高い精度を持つ「量子ビット」を実現した。既存の半導体集積化技術を用いた量子ビット素子実装が可能なため、大規模量子計算機の実現に向けた重要なステップになるとしている。 究極の大規模汎用量子コンピュータ実現法を発明

究極の大規模汎用量子コンピュータ実現法を発明

東京大学工学系研究科教授の古澤明氏と同助教の武田俊太郎氏は2017年9月22日、大規模な汎用量子コンピュータを実現する方法として、1つの量子テレポーテーション回路を無制限に繰り返し利用するループ構造の光回路を用いる方式を発明したと発表した。 予算なき量子コンピュータ開発、欧米より一桁低い日本を憂う

予算なき量子コンピュータ開発、欧米より一桁低い日本を憂う

今回は番外編として、量子コンピュータについて少し触れてみたい。日本が開発した量子コンピュータの原理を、いち早くハードウェアに実装したのは、カナダのD-Wave Systemsであった。