トポロジカル絶縁体で高性能純スピン注入源開発:BiSbをSOT-MRAMに応用

東京工業大学は、トポロジカル絶縁体であるBiSb(ビスマスアンチモン)の(012)面方位を用いて、高性能の純スピン注入源を開発した。次世代スピン軌道トルク磁気抵抗メモリ(SOT-MRAM)を実現できる可能性が高まった。

データの書き込み電流を1桁削減、記録速度は20倍に

東京工業大学工学院電気電子系のファム・ナム・ハイ准教授らによる研究チームは2018年7月、トポロジカル絶縁体であるBiSb(ビスマスアンチモン)の(012)面方位を用いて、高性能の純スピン注入源を開発したと発表した。この技術を応用して、記録速度や記録密度が極めて高く低電力のスピン軌道トルク磁気抵抗メモリ(SOT-MRAM)を実現することが可能になるという。

DRAMやSRAM、フラッシュメモリからの置き換えを可能にする次世代メモリとして、磁気抵抗メモリ(MRAM)が注目されている。現在は、データの書き込み技術としてSTT(Spin transfer torque)法を用いた製品が開発されている。この方式は、MTJ素子の磁化固定層から磁化自由層にスピン偏極電流を注入することで、磁化反転を起こす仕組みである。「書き込み時の電力消費が揮発性メモリに比べて1桁大きい」ことなどが、本格普及に向けた課題となっている。

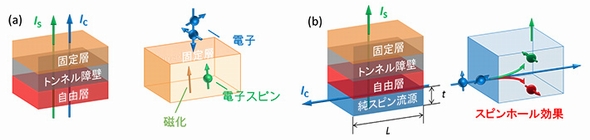

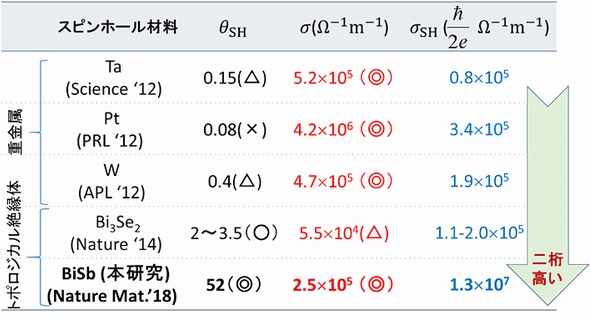

研究チームは今回、スピンホール効果で得られる純スピン流を、磁化自由層に注入すると発生するスピン軌道トルク(SOT:Spin orbit torque)を用いて磁化を反転させる技術に着目した。SOT法では、スピンホール効果のスピンホール角(θSH)が1より大きく、高い電気伝導性を示すスピンホール材料を用いると、MRAM素子の磁化反転に必要な電流を1桁、消費エネルギーを2桁以上も低減できることが分かっている。ただし、これまで研究されてきた重金属やバンドキャップが大きいトポロジカル絶縁体を用いたSOT法では、「スピンホール角が小さい」「電気伝導率が小さい」などの理由で、十分な性能が得られていなかったという。

そこで研究チームが注目したのは、バンドギャップが小さく、電気伝導率は高いBiSbである。分子線エピタキシャル法(MBE)を用いて、Sb組成比が0〜100%の全領域において系統的にBiSb薄膜の結晶成長を行い、電気伝導率が最大2.5×105Ω-1m-1と金属並みの特性を持つBiSbの製膜技術を確立した。併せて、垂直異方性磁界が50kOeのMnGa磁性薄膜と接合する技術も開発した。

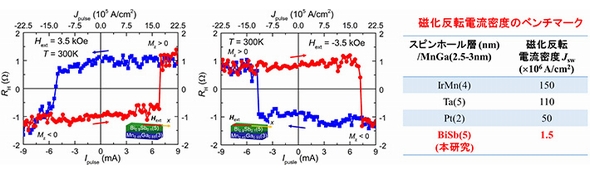

研究チームは、BiSbの(012)面とMnGaの接合において、BiSb(012)面のスピン軌道トルクを測定した。この結果、室温で最大52のスピンホール角を観測した。また、スピンホール伝導率は従来材料に比べて2桁も高い値となった。

さらに、BiSb/MnGa接合では、従来に比べて1〜2桁小さい電流密度で、MnGaのスピン軌道トルクによる磁化反転が生じていることが明らかとなった。これらの結果から、BiSbをスピン軌道トルク磁気抵抗メモリに応用すると、データ書き込みに必要な電流を1桁、消費エネルギーを2桁それぞれ低減し、記録速度は20倍、記録密度は1桁も向上できることが分かった。

研究チームは今後、産業界と連携してSOT-MRAMの早期実用化を目指す。これが実用化されると、機器のさらなる省エネ化を可能にするとともに、新たなメモリ市場として5〜10兆円規模の需要創出が期待できるとみている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「温めると8.5%も縮む」材料、東工大らが発見

「温めると8.5%も縮む」材料、東工大らが発見

東京工業大学は、「温めると縮む」負熱膨張材料の合成に成功した。光通信や半導体製造装置などに用いる材料の熱膨張を抑制することが可能となる。 東工大、5G向け小型フェーズドアレイ無線チップを開発

東工大、5G向け小型フェーズドアレイ無線チップを開発

東京工業大学の岡田健一准教授らは、5G(第5世代移動通信)システムに向けた28GHz帯フェーズドアレイ無線機チップを開発した。シリコンCMOS技術で実現しており、安価に量産が可能となる。 新しいダイヤモンド量子発光体、東工大らが作製

新しいダイヤモンド量子発光体、東工大らが作製

東京工業大学工学院電気電子系の研究グループは、スズ(Sn)を導入したダイヤモンドを高温高圧環境で処理することにより、スズと空孔(V)が結びついた新しい発光源(SnVカラーセンター)を形成することに成功した。量子ネットワークへの応用に期待できるとする。 指先に装着できる、CNTを用いた非破壊検査チップ

指先に装着できる、CNTを用いた非破壊検査チップ

東京工業大学らの研究グループは、材料にカーボンナノチューブ(CNT)膜を用いたテラヘルツ検査チップを開発した。検査チップを指先に取り付け、配管の亀裂検査などを非破壊で行うことが可能となる。 東工大、BLE受信機の消費電力を半分以下に

東工大、BLE受信機の消費電力を半分以下に

東京工業大学の研究グループは、消費電力が極めて小さいBLE(Bluetooth Low Energy)無線機の開発に成功した。これまでに報告されたBLE無線機に比べて、消費電力は半分以下だという。 ありふれた元素で窒化物半導体を開発、高性能化を実現

ありふれた元素で窒化物半導体を開発、高性能化を実現

東京工業大学と物質・材料研究機構(NIMS)の研究グループは、希少元素を含まない窒化銅(Cu▽▽3▽▽N)を用いて、高い伝導キャリア移動度を示すp型とn型の窒化銅半導体を開発することに成功した。