2D NANDと3D NANDのスケーリング(高密度化)手法:福田昭のストレージ通信(117) 3D NANDのスケーリング(5)

今回は、2D NANDフラッシュ(プレーナーNANDフラッシュ)と3D NANDフラッシュのスケーリング(高密度化)手法の違いについて解説する。

スケーリング(高密度化手法)のパラダイムシフト

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、3D NANDフラッシュメモリの断面構造と、メモリセルアレイの製造工程を説明した。今回は、2D NANDフラッシュ(プレーナーNANDフラッシュ)と3D NANDフラッシュのスケーリング(高密度化)手法の違いを解説する。

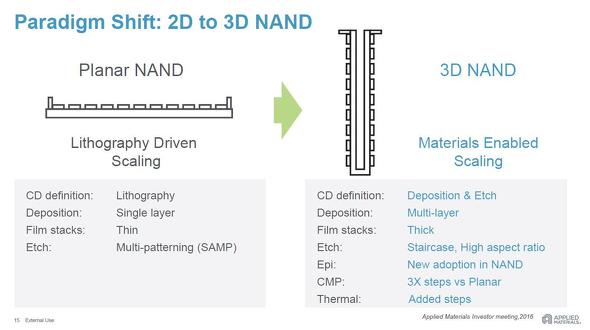

2D NANDフラッシュ(プレーナーNANDフラッシュ)のスケーリング(高密度化)手法(左)と3D NANDフラッシュのスケーリング(高密度化)手法のまとめ。上の構造図はセルストリングのイメージ。出典:Applied Materials(クリックで拡大)

2D NANDフラッシュ(プレーナーNANDフラッシュ)のスケーリング(高密度化)手法は、既存の半導体メモリと基本的には変わらない。リソグラフィ技術の改良による微細化、すなわち加工可能な寸法を細くすることで、メモリセルを小さくし、記憶密度を上げる。講演では「リソグラフィによって駆動されるスケーリング(Lithography Driven Scaling)」と呼んでいた。

プレーナーNANDフラッシュでは、最小の加工寸法(CD:クリチカルディメンション)は、リソグラフィ技術によって決まる。セルトランジスタの膜形成は1層ずつであり、1層分の薄膜は極めて薄い。そして微細加工には、自己整合型マルチパターニング(SAMP)技術によるエッチングが使われる。

これに対して3D NANDフラッシュのスケーリング(高密度化)手法は、微細化に頼らない。パラダイムシフトが起こっている。講演では「材料が可能にするスケーリング(Materials Enabled Scaling)」と呼んでいた。具体的には、多層(Multi-layer)構造の層数を増やすことによってメモリセルの積層数を増やし、記憶密度を上げる。ここで重要なのは、メモリセルを小さくしないことだ。メモリセルの大きさを変えずに、積み上げる数を増やす、というスケーリングである。

3D NANDフラッシュでは、最小の加工寸法は成膜技術とエッチング技術によって決まる。リソグラフィ技術ではない。セルトランジスタの膜形成は多層であり、1層分の薄膜はかなり厚い。微細加工の主役はエッチング技術であり、非常に高いアスペクト比で深い孔を作る技術と、階段状の構造(ステアケース)を作る技術が必要となる。またCMP(化学的機械的研磨)による平坦化技術が多用される。CMPのステップ数は、3D NANDフラッシュではプレーナーNANDフラッシュの3倍に達する。

(次回へ続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm世代のCMOSロジック製造技術によって記憶容量が40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果を、前後編で報告する。前編では、高温動作での読み出し電圧マージンの確保と、低温動作での書き込み電圧マージンの維持について紹介する。 膨張を続けるデジタルデータをNANDフラッシュが貯蔵

膨張を続けるデジタルデータをNANDフラッシュが貯蔵

2018年5月に開催された「IMW(International Memory Workshop)」のショートコースで行われた技術講座から、「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」の概要をシリーズでお届けする。 2D NANDフラッシュと3D NANDフラッシュのセルアレイ構造

2D NANDフラッシュと3D NANDフラッシュのセルアレイ構造

今回は2D NANDフラッシュ技術と3D NANDフラッシュ技術におけるメモリセルアレイ構造の違いを、より具体的に説明する。 3D NANDフラッシュメモリの断面構造と製造工程

3D NANDフラッシュメモリの断面構造と製造工程

2018年5月に開催された国際会議「IMW」で行われたセミナー「3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望」の概要をシリーズで紹介している。今回は、3D NANDフラッシュメモリの断面構造と、メモリセルアレイの製造工程を解説しよう。 光変調器を駆動する高速CMOS回路の試作事例

光変調器を駆動する高速CMOS回路の試作事例

今回は、光変調器を高速で駆動する電気回路、すなわちシリコンCMOSのドライバ回路を試作した事例を説明する。 100Gbpsを超える光ファイバー高速伝送へのアプローチ

100Gbpsを超える光ファイバー高速伝送へのアプローチ

今回は、100Gビット/秒(bps)と極めて高速な変調信号を光ファイバーで伝送する実験結果を紹介する。