3D NANDフラッシュ製造のカギとなるプロセス技術:福田昭のストレージ通信(118) 3D NANDのスケーリング(6)

今回は、3D NANDフラッシュメモリの製造プロセスにおける重要な技術(キープロセス)について解説する。

高難度の技術を駆使して3D NANDの複雑な立体構造を実現

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、2D NANDフラッシュ(プレーナーNANDフラッシュ)と3D NANDフラッシュのスケーリング(高密度化)手法の違いを説明した。今回は、3D NANDフラッシュメモリの製造プロセスにおける重要な技術(キープロセス)を概観する。

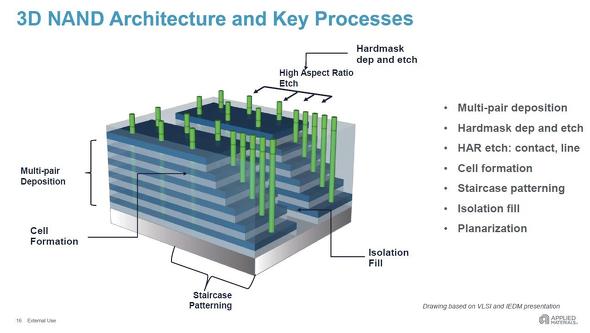

「キープロセス」には、「多ペア薄膜(Multi-pair)の成膜(Deposition)」「ハードマスク(Hardmask)の成膜とエッチング」「高アスペクト比(HAR:High Aspect Ratio)のエッチング」「メモリセルの形成(Formation)」「ステアケース(Staircase)のパターン形成」「絶縁膜の埋め込み(Isolation Fill)」「平坦化(Planarization)」などがある。これらの中で特に注目すべきプロセスを、ごく簡単に説明していこう。

ペア薄膜とは、絶縁層と制御ゲート層(ワード線層)の薄膜のことで、3D NANDフラッシュの製造では、このペア薄膜を数多く積み上げることで、セルストリングを垂直方向に形成する。数多くのペア薄膜を均一な品質と膜厚で堆積することが欠かせない。

エッチングのマスクパターンは通常、リソグラフィ(レジストを露光・現像すること)によって形成する。これに対して薄膜を堆積してエッチングによってパターンを作り、このパターンをさらに下層のエッチング用マスクとする手法がある。これが「ハードマスク」である。

3D NANDフラッシュのセルストリング形成プロセスでは、非常に深くて細い孔をエッチングによって開けるため、頑丈なハードマスクを使う。ここで孔の深さ(高さ)と直径の比率が「アスペクト比(AR)」である。セルストリング用の孔は例えば32ペア層といった極めて多くの層を貫通するので、エッチングは当然ながら、超HARとなる。

メモリセルの形成で重要なのは、細長い孔の形成だけでなく、孔を形成した後に窒化膜や酸化膜などを孔の側壁に均一に成膜することである。これは容易ではなく、原子層単位の膜厚制御が求められる。

ステアケース(階段状の構造)のパターン形成も、3D NANDフラッシュに特有の製造工程である。例えば32ペアのメモリセルを積み上げる構造では、32段の階段構造を作り、さらには最上層の金属配線層とステアケース各段のワード線層を細長い柱状の導体で接続しなければならない。

忘れてはならないのが、絶縁膜の埋め込み工程である。複雑で入り組んだ形状の構造に、絶縁膜をすき間なく充填する必要がある。そしてリソグラフィによってパターンを形成する前には、表面をあらかじめ平坦化しておかければならない。前回でも説明したように、形状が複雑な3D NANDフラッシュの製造では、平坦化プロセス(CMPプロセス)の回数が著しく増加する。

(次回へ続く)

⇒「福田昭のストレージ通信」連載バックナンバー

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

膨張を続けるデジタルデータをNANDフラッシュが貯蔵

膨張を続けるデジタルデータをNANDフラッシュが貯蔵

2018年5月に開催された「IMW(International Memory Workshop)」のショートコースで行われた技術講座から、「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」の概要をシリーズでお届けする。 2D NANDフラッシュの限界と3D NANDフラッシュへの移行

2D NANDフラッシュの限界と3D NANDフラッシュへの移行

今回は、2D NANDフラッシュメモリの記憶容量が拡大していった経緯と、2D NANDフラッシュ技術から3D NANDフラッシュ技術への転換について解説する。 2D NANDフラッシュと3D NANDフラッシュのセルアレイ構造

2D NANDフラッシュと3D NANDフラッシュのセルアレイ構造

今回は2D NANDフラッシュ技術と3D NANDフラッシュ技術におけるメモリセルアレイ構造の違いを、より具体的に説明する。 光送受信システムのリンクバジェット計算事例

光送受信システムのリンクバジェット計算事例

今回は、光送受信システムのリンクバジェットを計算した事例を説明する。 光変調器を駆動する高速CMOS回路の試作事例

光変調器を駆動する高速CMOS回路の試作事例

今回は、光変調器を高速で駆動する電気回路、すなわちシリコンCMOSのドライバ回路を試作した事例を説明する。 896Gbpsの伝送帯域を実現する超高速光送受信モジュール(前編)

896Gbpsの伝送帯域を実現する超高速光送受信モジュール(前編)

今回は、16チャンネルの光送受信モジュール(光トランシーバー)の試作例を紹介する。試作した光トランシーバーは、1チャンネル当たり56Gbpsの速度で光信号を変調する。つまり、16チャンネルの合計では、896Gbpsの帯域幅を実現できることになる。