Intel、EUVの準備は整ったが課題も:適用するノードは明らかにせず

IntelのEUV(極端紫外線)プログラムの責任者であるBritt Turkot氏は、「EUVリソグラフィは導入の準備ができており、技術開発に向けた量産体制に入っている」と述べた。しかし、「複雑で高額なシステムを利用して最先端のチップを量産するには、依然としていくつかの課題がある」とも述べている。

IntelのEUV(極端紫外線)プログラムの責任者であるBritt Turkot氏は、「EUVリソグラフィは導入の準備ができており、技術開発に向けた量産体制に入っている」と述べた。しかし同氏は、「複雑で高額なシステムを利用して最先端のチップを量産するには、依然としていくつかの課題がある」とも述べている。

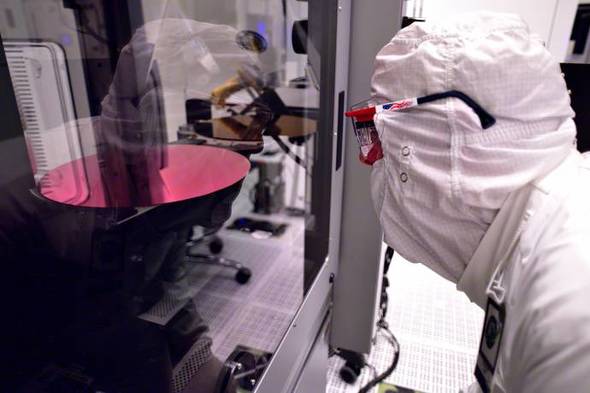

IntelのフェローでEUV担当ディレクタを務めるTurkot氏によると、米国オレゴン州ポートランドにある同社の工場では、居室サイズのシステムが稼働しているという。同氏は、現在量産している10nm製品や、開発を計画している7nmノードに、EUVを適用するのかどうか、適用するならばどう適用するのかについては明らかにしなかった。

Intelは、20年以上前からEUV開発に携わってきた半導体メーカーの1社だが、同技術の適用については後じんを拝する形となった。同社のライバルであるSamsung ElectronicsとTSMCはそれぞれ2018年に、7nmプロセスにEUVを適用すると発表している。

ただし、2つの情報筋が「TSMCの『N7+』プロセスは、4つのメタル層にのみEUVを適用している」と述べていることから、同社のEUV技術には課題が残ると推察される。つまりTSMCは、複数のメタル層には、従来の液浸ステッパーによるダブルパターニングを適用していると考えられる。

ある匿名の情報筋は、「TSMCは、スループットや同社が所有するEUVマシンの台数、コスト的なトレードオフの観点からこのような決断に至ったと思われる。一方、SamsungはEUVマシンに、より多額の投資を行った可能性が高い」と述べていた。

EUVシステムは、1台当たり約1億5000万米ドルのコストが掛かる。しかも商用生産には、複数のEUVシステムが必要だ。

TSMCの広報担当者は、「確かに、多くの層にダブルパターニングを適用している」と認めているが、N7+ノードの何層のメタル層にEUVを適用しているかについては明らかにしていない。同氏は、「さまざまなことを検討した上で、液浸ダブルパターニングとEUVを併用することを決断した。液浸ダブルパターニングに対するEUVのコストと成熟度は、非常に重要な検討要素だ」と述べている。

一方、ある情報筋によると、SamsungはEUVを適用した7nmノードの価格を積極的に引き下げ、一部の新興企業に、競合他社のマルチレイヤーマスク(MLM)よりも安い価格でフルマスクセットを提供しているという。TSMCは、少量生産のコストを削減するために2007年にMLMマスクセットを導入している。MLMマスクセットの価格は、フルマスクセットの約60%と言われている。

Samsungは、同社のファウンドリーの構築に掛かったコストやEUVの適用方法については明らかにしていない。Samsungのある幹部は、Intelの10nmプロセスの開発が遅れたのは、アクティブ領域のゲートコンタクト形成(COAG:Contact Over Active Gate)を野心的に進めたことが原因だと推察しているという。この幹部は、「Samsungは、段階的にCOAGに移行する計画だ」と述べたが、詳細は語らなかった。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか

10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか

Intelは2016年以降、今日に至るまで、10nmプロセスを立ち上げることができていない。一方で、配線ピッチは同等であるはずの、TSMCとSamsung Electronicsの7nmプロセスは計画通りに進んでいる。ではなぜ、Intelは10nmプロセスの立ち上げに苦戦しているのだろうか。 高温下でも高信頼性のLDMOSプロセス技術を開発

高温下でも高信頼性のLDMOSプロセス技術を開発

東芝デバイス&ストレージとジャパンセミコンダクターは、車載用アナログパワーICなどの用途に向け、高温環境下でも高い信頼性を実現可能な、LDMOSプロセス技術を開発した。 Samsung、3nm GAAのリスク生産を2020年にも開始か

Samsung、3nm GAAのリスク生産を2020年にも開始か

Samsung Electronicsのファウンドリー部門は、2019年5月14日(米国時間)に米国で開催した「Samsung Foundry Forum 2019 USA」において、次世代の3nm GAA(Gate-All-Around)技術に向けた最初のプロセスデザインキットを含め、プロセス技術のロードマップをアップデートした。 Intelが7nm開発にメド、2021年に市場投入を予定

Intelが7nm開発にメド、2021年に市場投入を予定

Intelの経営幹部は、同社の投資家向けの年次ミーティングにおいて「当社の10nmプロセッサは、これまで出荷予定に遅れが生じていたが、今回は、2018年に発表したスケジュール通り、2019年6月に出荷を開始できる見込みだ」と述べた。7nmプロセッサの出荷を2021年に予定していることも明らかにした。 Samsungが5nmプロセスの開発を完了、2020年に量産

Samsungが5nmプロセスの開発を完了、2020年に量産

Samsung Electronics(以下、Samsung)は、EUV(極端紫外線)を用いた5nmプロセスの開発が完了し、受注を開始したと発表した。 3nm止まりか1nmか、微細化はレジスト開発が鍵

3nm止まりか1nmか、微細化はレジスト開発が鍵

半導体リソグラフィ技術に関する国際会議「SPIE Advanced Lithography 2019」で行われたパネルセッションの中で、エンジニアたちは、「半導体ロードマップはこの先、10年間延長して1nmプロセスまで実現できる可能性もあれば、新しいレジスト材の不足によって、3nmプロセスで行き詰まる可能性もある」と、希望や不安について語った。