小型・薄型・低コストのパッケージを実現する組み立て技術:福田昭のデバイス通信(216) 2019年度版実装技術ロードマップ(27)(2/2 ページ)

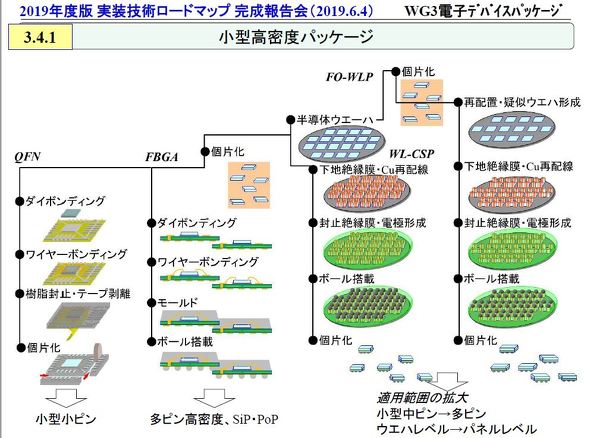

今回から、パッケージの組み立てプロセスの技術動向を紹介する。まずは、QFN、BGA、WL-CSP、FO-WLPの組み立て工程を取り上げる。

QFN、BGA、WL-CSP、FO-WLPの組み立て工程

QFNの組み立てフロー(組み立て工程)は以下のように進む。回路を作り込んで検査を完了したウエハー(完成ウエハー)の裏面をまず研削する(裏面研削)。次にダイヤモンドブレードによって完成ウエハーを個別のダイ(チップ)に切り分ける(個片化)。それからダイの裏面をリードフレームに接着する(ダイボンディング)。続いてパッケージの電極とダイの電極を金属ワイヤ(Auワイヤなど)によって結線する(ワイヤボンディング)。それから全体を樹脂で封止する(樹脂封止)。1枚のリードフレームは数十個のチップを搭載するので、樹脂封止も数十個のチップを一括して実施する。最後に樹脂封止したパッケージを1個ずつ切り分け(個片化)、テスト工程に回す。

FBGA/BGAの組み立てフローは以下のようになる。完成ウエハーを裏面研削して個片化するまではQFNと同じである。次にパッケージ基板(多層樹脂基板)にダイの裏面を接着する。続いてダイの電極とパッケージ基板の電極を金属ワイヤによって結線する。1枚のパッケージ基板には数十個〜数百個のダイが載っている。この全体を樹脂で封止する。次にパッケージ基板の裏面(底面)に、はんだボールを搭載する。それから個別のパッケージに切り分け、検査工程に回す。

WL-CSPとFO-WLPの組み立てフローは以下のように進む。WL-CSPは完成ウエハーのままでパッケージを作製する。FO-WLPは完成ウエハーを個片化し、ダミーウエハーにダイを再配置してからパッケージを作製する。以下の工程は、両者でほぼ同じである。まずウエハーに下地絶縁膜と銅の再配線層を形成する。続いて封止絶縁膜と電極を作る。次に、はんだボールを搭載する。それから個別のパッケージに切り分ける。

FO-WLPの組み立てには、詳細の異なる複数の技術が存在する。次回は組み立てフローの異なる、いくつかのFO-WLP組み立て技術を説明する予定だ。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

5Gの移動通信システムを支えるミリ波のパッケージ技術

5Gの移動通信システムを支えるミリ波のパッケージ技術

今回は、第5世代(5G)の移動通信システムに向けたミリ波対応のSiP(System in Package)技術を紹介する。ミリ波帯向けでは、アンテナとFEM(Front End Module)を積層した「AiP(Antenna in Package)というSiPの実用化が始まっている。 1個のパッケージでシステムを実現するSiP

1個のパッケージでシステムを実現するSiP

今回は、SiP(System in Package)を実現する幾つかの手法のうち、2.X次元(2.XD)の実装技術を解説する。ここでカギとなるのは、インタポーザだ。 パッケージの多端子化と小型化、薄型化、低コスト化が進む

パッケージの多端子化と小型化、薄型化、低コスト化が進む

今回は第3章「電子デバイスパッケージ」から、各種パッケージの技術動向を紹介する。半導体パッケージの歴史は、多端子化と小型化、薄型化、低コスト化の歴史でもある。 Intelが3つの次世代パッケージング技術を明らかに

Intelが3つの次世代パッケージング技術を明らかに

Intelは、米国カリフォルニア州サンフランシスコで2019年7月9〜11日の日程で開催されている「SEMICON West 2019」に合わせて行われたイベントにおいて、3種類のパッケージング技術に関する同社のロードマップを初めて明らかにした。 2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。