ラティス、28nmFD-SOIの新FPGAプラットフォーム:「エッジAIに最適」と強調(2/2 ページ)

Lattice Semiconductor(ラティスセミコンダクター)は2019年12月10日(米国時間)、28nm FD-SOI(完全空乏型シリコン・オン ・インシュレーター)を採用した新たな低消費電力FPGAプラットフォーム「Nexus」および、その最初の製品となる「CrossLink-NX」を発表した。

低消費電力、高信頼性、ハイパフォーマンス、小型化

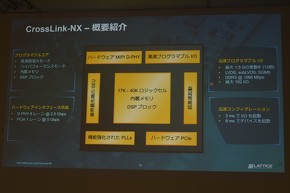

Nexusの第1弾製品が「CrossLink-NX」だ。

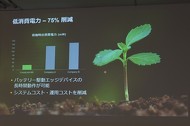

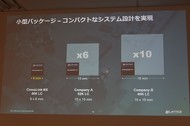

ロジックセルサイズが17Kの「CrossLink-NX-17」と40Kの「CrossLink-NX-40」の2つがあり、前述のように低消費電力とハイパフォーマンスモードを選択可能となほか、競合の同クラスFPGAと比較し最大75%低い消費電力、最大100倍のソフトエラーレートに対する信頼性、10分の1の小型パッケージを実現したとしている。

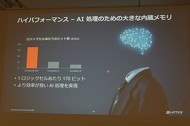

また、1ロジックセル当たり170ビットと「同クラス最高のメモリ−ロジック比率」(同社)となっており、既存の同社製品と比較し2倍の性能を実現。「より効率の良いAI処理を実現する」という。

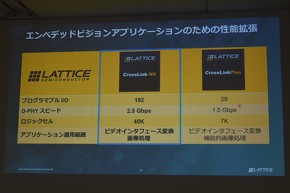

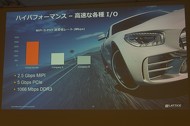

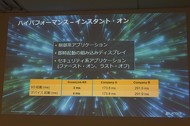

2.5Gビット/秒のMIPI D-PHYや5Gビット/秒のPCIeをハードウェアロジックとして搭載しているほか、プログラマブルIOとして1.5Gビット/秒で動作する作動インタフェースを12ペア搭載。IOの数は最大192となっている。さらに、高速起動、産業用モーター制御など、長い起動時間が許容できないアプリケーションをサポートするため、IOブロックは3ミリ秒以内に起動をできるうえ、デバイス全体の起動も15ミリ秒以内で可能とした。

Chen氏は、これらの性能向上によって、複数センサーや複数ディスプレイのサポート、高解像度、高フレームレート、MIPIと従来のインタフェースの接続、そして低消費電力でのエッジAI処理、といった組み込み市場のトレンドに対応できる、と説明した。CrossLink-NXは既にサンプル提供中だが、量産出荷については2020年末ころを予定しているという。

同社はCrossLink-NXの発表にあたり、FPGA開発ソフトウェア最新バージョン「Radiant 2.0」の提供も開始。オンチップデバッグやタイミング解析ツール、ECOエディタ、シグナルインテグリティ解析などの新たな機能によって、「FPGAの開発をより早く、より簡単に行うことができる」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

電池駆動も可能な超低消費電力AI、Latticeが展示

電池駆動も可能な超低消費電力AI、Latticeが展示

2019年10月15〜18日にかけて、「CEATEC 2019」が千葉・幕張メッセで開催される。Lattice Semiconductor(ラティスセミコンダクター)は、同社の最新FPGAやソリューションを展示する。 低電力FPGA、セキュリティやAI機能を強化

低電力FPGA、セキュリティやAI機能を強化

Lattice Semiconductor(ラティスセミコンダクター)は、セキュリティ機能を強化したFPGA「MachXO3D」と、エッジ製品にAI機能を搭載するための技術スタック「sensAI」新バージョンを発表した。 ラティス、FPGAベースのAIスタックを拡張

ラティス、FPGAベースのAIスタックを拡張

Lattice Semiconductor(ラティスセミコンダクター)は、エッジ製品側にAI(人工知能)機能を導入するための技術スタック「Lattice sensAI」について、その機能拡張を発表した。 低電力で低コスト、FPGAを活用したAIスタック

低電力で低コスト、FPGAを活用したAIスタック

Lattice Semiconductor(ラティス・セミコンダクター)は、極めて小さい電力消費と部材コストで、エッジ製品へのAI(人工知能)導入を行うことができる技術スタック「Lattice sensAI」を発表した。 エッジコンピューティング、低電力でAI実現

エッジコンピューティング、低電力でAI実現

AI(人工知能)技術をベースとしたエッジコンピューティングを次の成長ドライバーと位置付けるLattice Semiconductor。フォーカスする分野は消費電力が1W以下で、処理性能は1テラOPS(Operations Per Second)までのアプリケーションだ。 超小型FPGAをエッジに、独自路線を進むLattice

超小型FPGAをエッジに、独自路線を進むLattice

小型で低消費電力のFPGAを手掛けるLattice Semiconductorは、クラウド市場に注力する他のFPGAベンダーとは明確に路線を分け、エッジ向けに力を入れる。