連載

部品内蔵基板の組み立て技術:福田昭のデバイス通信(219) 2019年度版実装技術ロードマップ(30)(3/3 ページ)

今回は、部品内蔵基板の組み立て工程を紹介する。半導体チップをフェースダウン(回路面を下にした状態)で基板に搭載する技術、フェースアップ(回路面を上にした状態)で基板に搭載する技術、微細な配線を形成できる技術の3つについて解説したい。

微細配線を形成可能な部品内蔵基板

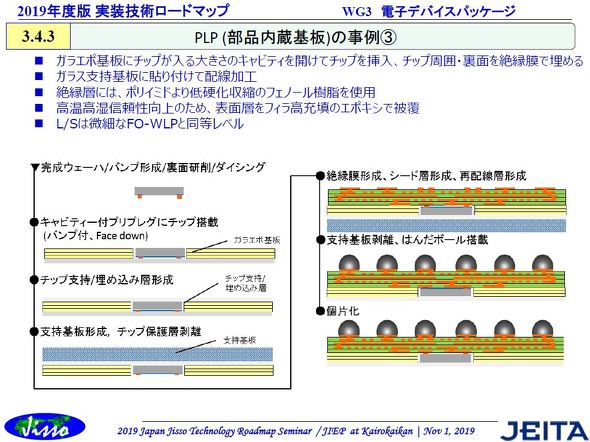

最後は、微細な配線を形成可能な部品内蔵基板の組み立て技術を紹介する。完成ウエハーの回路面にCuバンプを形成し、ウエハーの裏面を研削し、シリコンダイを切り出す。シリコンダイ搭載用のキャビティー(空洞)を形成済みのガラスエポキシ基板(ガラエポ基板)の底面にシリコンダイ保護層を貼る。続いてシリコンダイをフェースダウンでガラエポ基板のキャビティー内に仮配置し、シリコンダイとガラエポ基板のすき間を誘電体材料で埋める。シリコンダイの裏面側に支持基板(ガラス基板など)を貼り付け、表面側の保護層を剥がす。

それからチップファーストの微細配線FO-WLP(組み立て技術のイメージ図)の組み立て工程と同様に、再配線層を形成する。再配線層の形成が完了したら、支持基板を剥離し、はんだボールを搭載する。最後に個別のパッケージあるいはモジュールとしてガラエポ基板を個別に切り分ける。再配線層の線幅/間隔は2μm〜5μm/2μm〜5μmと狭い。ただしガラエポ基板は寸法が例えば500mm×400mmとシリコンウエハーの直径300mmよりも大きいので、反りを抑える対策が必須である。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

微細配線が可能なFO-WLPの組み立て技術

微細配線が可能なFO-WLPの組み立て技術

前回に続き、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。今回は、微細配線を形成可能なFO-WLPを取り上げる。 多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術

多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術

パッケージの組み立てプロセス技術を紹介している。今回は、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。 小型・薄型・低コストのパッケージを実現する組み立て技術

小型・薄型・低コストのパッケージを実現する組み立て技術

今回から、パッケージの組み立てプロセスの技術動向を紹介する。まずは、QFN、BGA、WL-CSP、FO-WLPの組み立て工程を取り上げる。 2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。 クロスポイント化に期待がかかる抵抗変化メモリ(ReRAM)

クロスポイント化に期待がかかる抵抗変化メモリ(ReRAM)

今回は抵抗変化メモリ(ReRAM)を解説する。ReRAMの原理の他、記憶密度を向上させる手段について説明する。 磁気抵抗メモリ(MRAM)の技術動向と製品動向

磁気抵抗メモリ(MRAM)の技術動向と製品動向

今回は、MRAMの技術開発状況と製品化動向を取り上げる。特に、最近のMRAM開発で注目されている埋め込みメモリについて解説する。