周辺回路とセルアレイを積層して3D NANDの密度をさらに高める:福田昭のストレージ通信(187) アナリストが語る不揮発性メモリの最新動向(14)(2/2 ページ)

今回は、周辺回路とメモリセルアレイを積層することによって3D NANDフラッシュの記憶密度をさらに高める技術を説明する。

周辺回路をセルアレイ直下のシリコンにあらかじめ形成

ここで考え出されたのが「空き地」の有効活用である。メモリセルアレイの直下にある「空き地」に周辺回路の一部だけでも作り込めば、シリコンダイの面積を削減できる。記憶密度が向上し、製造コストが下がる。このアイデアを具現化したのが、MicronとIntelの連合である。始めの世代では周辺回路のごく一部をメモリセルアレイの下に作り込んだ。これがうまくいくと、次の世代からは周辺回路の大半をメモリセルアレイの直下にレイアウトした。両社はこの技術を「CUA(CMOS Under Array)」と呼んでいる。

MicronとIntelの連合は、メモリセルの記憶技術にフローティングゲート(FG)方式を採用している。3D NANDフラッシュでは独自と言って良い技術だ。このため、CUAはFG方式に特有の技術と見られたこともあった。しかし実際には、記憶技術にチャージトラップ(CT)方式を採用している他社の3D NANDフラッシュでも、類似の技術を導入し始めた。まずSK hynixが、「PUC(Periphery Under Cell array)」と呼んで類似の技術を製品化した。名称は異なるものの、基本的にはCUAと同じ技術である。周辺回路をシリコンウエハーに作り込んでから、その上にメモリセルアレイを形成する。

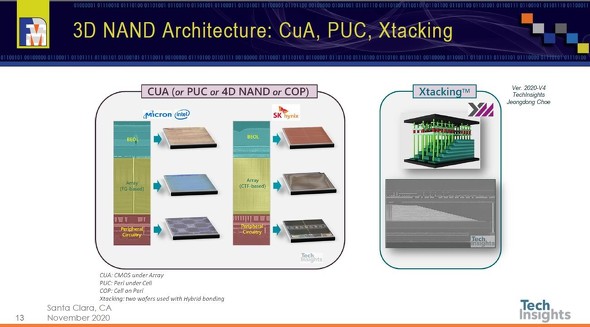

CUA技術とPUC技術が抱える問題の一つに、メモリセルアレイの形成プロセスによる熱処理が周辺回路の動作性能(トランジスタ性能)を劣化させる恐れがある。この問題を嫌ったのがYMTCの「Xtacking(エクスタッキング)」技術だ(参考記事:「中国の3D NANDフラッシュメーカー「YMTC」の現状」)。周辺回路とメモリセルアレイを異なるシリコンウエハーに形成し、シリコンウエハーを張り合わせることで周辺回路とメモリセルを積層する。

3D NANDフラッシュメモリの周辺回路とメモリセルアレイを積層する技術の概念図。左が「CUA」、中央が「PUC」、右が「Xtacking」である。シリコンダイを電子顕微鏡で観察した画像を併載している。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

シリコン面積に占めるセルアレイの比率は約10ポイント向上

3D NANDフラッシュのシリコンダイ面積に占めるメモリセルアレイ領域の割合(セルアレイ効率)を大手ベンダー各社で比較すると、周辺回路とセルアレイを積層することの効果が把握できる。Choe氏は講演で、32層〜128層の3D NANDフラッシュのセルアレイ効率を比較したスライドを示していた。CUA(および類似の技術)を採用したシリコンダイはセルアレイ効率が90%前後と高い。これに対してCUAを導入していないシリコンダイは、セルアレイ効率が最大でも80%前後にとどまっている。CUAの導入によってセルアレイ効率は約10ポイント、高まっていることが分かる。

3D NANDフラッシュのシリコンダイ面積に占めるメモリセルアレイ領域の割合(セルアレイ効率)。周辺回路とメモリセルアレイを積層したダイでは、セルアレイ効率が高い。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

CUAおよびPUCに類似の技術は今後、Samsung Electronics、キオクシア-Western Digital連合でも次世代以降の製品に採用していくとみられる。3D NANDフラッシュ業界全体の共通技術となっていくだろう。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。