NVIDIA、ArmベースのCPU「Grace」を発表:データセンター向け

NVIDIAは2021年4月12日(米国時間)、データセンター向けCPU「Grace」を発表し、CPU市場に正式に参入した。同CPUは、大規模なAI(人工知能)やHPC(ハイパフォーマンスコンピューティング)市場向けに、GPUと組み合わせる設計となっている。

NVIDIAは2021年4月12日(米国時間)、データセンター向けCPU「Grace」を発表し、CPU市場に正式に参入した。同CPUは、大規模なAI(人工知能)やHPC(ハイパフォーマンスコンピューティング)市場向けに、GPUと組み合わせる設計となっている。

NVIDIAのCEOであるJensen Huang氏は、同社が開催中の「GPU Technology Conference(GTC)」の基調講演で、「今日、われわれは現代のデータセンターの基本構成要素となる、新しいコンピュータを紹介する」と語った。「Graceは、最新のGPUアクセラレーションコンピューティング、Mellanoxの高性能ネットワーキングに続く、“パズルの最後のピース”となる」(Huang氏)

GPT-3のような巨大な自然言語処理(NLP)AIモデルは、膨大な計算能力を必要としており、モデルのサイズや複雑さの増大は、データセンターやクラウドにおいて、これまでよりもさらに強力なAIコンピュータの需要を後押ししている。

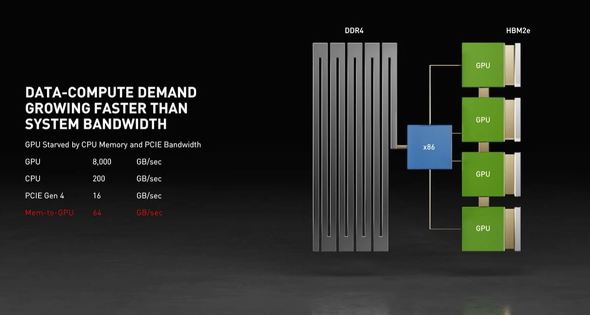

GPUは、高いメモリ帯域幅を持つ高速な計算のために設計されているが、メモリとGPUの間にあるCPUが、データをGPUに送信する際に、しばしばボトルネックになるとHuang氏は説明する。同氏は、GPUのメモリに収まりきらないほど巨大なAIモデルを想定したトレーニングシステムについて説明した。「典型的なシステムでは、4つのGPUと、それぞれ2Tバイト/秒で動作する、合計80Gバイトの超高速メモリが搭載されていることが多い。GPUの横には、わずか0.2Tバイト/秒で動作する1Tバイトのメモリを搭載したCPUがある。CPUのメモリはGPUの3倍の大きさだが、速度は40倍も遅いのだ」(Huang氏)

CPUと各GPU間において、より高速なメモリと専用の通信チャンネルがあれば、こうした状況は改善するが、PCIe(PCI Express)がボトルネックとなる。GPU間の通信向けに設計された「NVLink」を用いる方法もあるが、NVLinkをサポートするx86ベースのCPUはない。

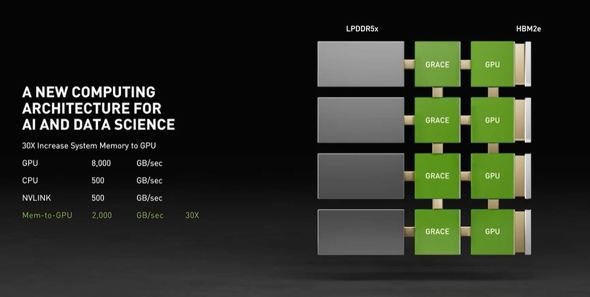

米国のコンピュータプログラミングの先駆者であるGrace Hopper氏にちなんで名付けられたNVIDIAのGraceは、NVLinkを4チャンネル備え、NVIDIAのGPU間との間で900Gバイト/秒の双方向通信を達成したとする。

Graceでは、LPDDR5を採用。LPDDR5は、DDR4に比べて2倍の帯域幅と、10倍のエネルギー効率を実現する。LPDDR5はモバイルの世界では既に普及しているが、NVIDIAは、パートナー各社との協力を通じて、ECC(誤り訂正符号)や冗長性といったメカニズムによって、サーバでも採用できるような信頼性を実現したとする。

これらにより、Graceベースのシステムは、x86 CPUで実行される現在の最先端の「NVIDIA DGX」ベースのシステムに比べ、1兆パラメーターのNLPモデルを10倍高速にトレーニングできるとする。

Graceは、Armの「Neoverse」コアをベースにしている。Huang氏は基調講演で「GraceはArmアーキテクチャの素晴らしさを際立たせている」と語った。「ArmのIP(Intellectual Property)があったからこそ、われわれは(AIやHPCといった)アプリケーションに最適化したCPUを開発することができた」(Huang氏)

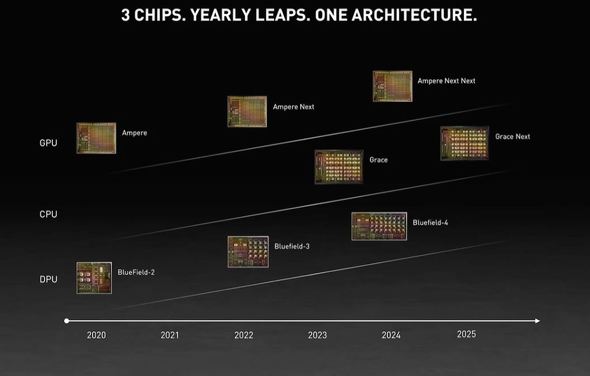

NVIDIAは2020年9月、Armの買収を発表したが、Huang氏によればGrace開発のプロジェクトはそれ以前から始まっていたという。NVIDIAは既に、同社のDPU(Data Processing Unit)の「BlueField」でArmコアを採用している。

なお、スイス国立スーパーコンピューティングセンター(CSCS)と米国エネルギー省のロスアラモス国立研究所は、Graceを搭載したスーパーコンピュータを構築する計画を発表した。

【翻訳、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

半導体業界に巨大M&Aの波が再来

半導体業界に巨大M&Aの波が再来

数年に一度、大きなM&Aの波が来る」といわれてきた半導体業界だが、2015年あたりからは毎年のように度肝を抜くようなM&Aが続いている。もちろん、事業部門の買収/売却も含めて半導体業界のM&Aはずっと続いてきたが、業界を揺るがすような、場合によっては業界関係者が今後に不安を抱くような大型M&Aが過去5年間で増えているのではないか。 NVIDIAのArm買収、大手3社が反対を表明か

NVIDIAのArm買収、大手3社が反対を表明か

2021年2月12日夜遅く(米国時間)に報じられたところによると、NVIDIAによるArmへの400億米ドルでの買収提案に対し、大手技術メーカー3社が反対を表明したという。この買収は、過去最大規模となる極めて重要な技術取引の1つであり、クラウドからエッジに至るまで幅広い影響を及ぼすとされている。 Intelの第3世代「Xeon SP」、AI性能や暗号化を強化

Intelの第3世代「Xeon SP」、AI性能や暗号化を強化

Intelは2021年4月6日、10nmプロセスを採用した第3世代の「Intel Xeon スケーラブル・プロセッサ(SP)」(開発コード名:Ice Lake)を発表した。1〜2ソケット向けの製品で、CPUコアには新しい世代の「Sunny Cove」を採用し、最大40コアを搭載する。前世代品と比較して、性能が46%向上しているとする。 Armが新アーキテクチャ「v9」を発表、セキュリティを強化

Armが新アーキテクチャ「v9」を発表、セキュリティを強化

Armは2021年3月30日(英国時間)、新しいアーキテクチャ「Armv9」を発表した。64ビット化された現行のアーキテクチャ「Armv8」から10年を経て発表された、最新のアーキテクチャとなる。 NVIDIAのMellanox買収、中国の承認取得で完了間近

NVIDIAのMellanox買収、中国の承認取得で完了間近

NVIDIAは、データセンター向けインターコネクト企業であるイスラエルのMellanox Technologies(以下、Mellanox)を69億米ドルで買収する計画に対して、中国当局の承認を得たことを発表した。中国当局の承認の獲得は、この取引における最後のハードルとなっていた。