東芝、SiC MOSFETのデバイス構造を最適化:高温環境下で高信頼と電力損失低減

東芝デバイス&ストレージは、SiC(炭化ケイ素)MOSFETの新たなデバイス構造を開発した。新構造を採用することで、高温環境下における素子の信頼性向上と電力損失の低減を実現した。

175℃の環境で、導通可能な電流量は従来構造の2倍以上に

東芝デバイス&ストレージは2021年6月、SiC(炭化ケイ素)MOSFETの新たなデバイス構造を開発したと発表した。新構造を採用することで、高温環境下における素子の信頼性向上と電力損失の低減を実現した。

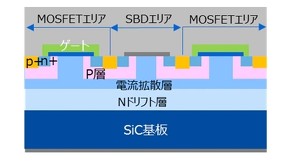

同社は、SiCパワー半導体の信頼性をさらに高めるため、新たなデバイス構造の開発に取り組んできた。2020年には、耐圧1.2kVのSiC MOSFETの内部に、SBD(ショットキーバリアダイオード)をPNダイオードと並列に配置した構造を発表した。

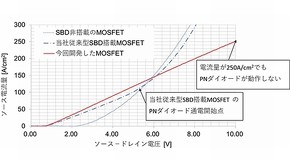

配置したSBDは、PNダイオードよりもオン電圧が低いため、電流はSBD側に流れる。これによって、PNダイオードへの通電を抑止し結晶欠陥の拡張を防いでいた。ただ、このデバイス構造を高耐圧のデバイスに適用すると、175℃以上の高温環境下では、導通可能な電流量に制限があったという。

そこで今回、従来のデバイス構造をベースに素子を約25%微細化し、SBDによるPNダイオードへの通電抑制能力を強化するなど、構造の最適化を行った。新構造を採用した耐圧3.3kVの素子を、175℃の高温環境下で動作させたところ、信頼性を維持しつつ、導通可能な電流量が従来構造品に比べて2倍以上となった。室温における単位面積当たりのオン抵抗は、耐圧3.3kVの素子で約2割、同1.2kVの素子で約4割、それぞれ低減できることを確認した。

東芝デバイス&ストレージは、新開発のデバイス構造を用いた耐圧3.3kV製品について、2021年5月よりサンプル出荷を始めている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

高耐圧LDMOSの静電破壊耐量と電力効率を両立

高耐圧LDMOSの静電破壊耐量と電力効率を両立

東芝デバイス&ストレージとジャパンセミコンダクターは2021年6月、車載アナログIC向け高耐圧LDMOSの「静電破壊耐量」と「電力効率」を両立させる技術を開発した。 東芝、ソリッドステートLiDAR向け受光技術を開発

東芝、ソリッドステートLiDAR向け受光技術を開発

東芝は、「ソリッドステート式LiDAR」向けの受光技術と実装技術を新たに開発した。新技術を採用すると、200mの最長測定距離を維持しつつ、従来に比べサイズが3分の1で、解像度は4倍となるLiDARを実現できるという。 東芝、トリプルゲートIGBTとゲート制御技術を開発

東芝、トリプルゲートIGBTとゲート制御技術を開発

東芝は、スイッチング損失を全体で最大40.5%も低減できる「トリプルゲートIGBT」を開発した。再生可能エネルギーシステムや電気自動車(EV)などに搭載される電力変換器の高効率化に向けて、早期実用化を目指す。 量子技術の産業化を加速、日本企業11社が協議会設立

量子技術の産業化を加速、日本企業11社が協議会設立

東芝、富士通、トヨタ自動車などの民間企業11社は2021年5月31日、量子技術の研究開発と社会実装の加速を目指す協議会「量子技術による新産業創出協議会」の設立発起人会を開催した。 東芝、SiCモジュール向けパッケージ技術を開発

東芝、SiCモジュール向けパッケージ技術を開発

東芝デバイス&ストレージは、SiC(炭化ケイ素)モジュール向けパッケージ技術を開発したと発表した。従来のパッケージ技術に比べ、面積を約20%削減でき、製品の信頼性は2倍に向上するという。 加賀東芝に300mmウエハー対応製造ラインを導入へ

加賀東芝に300mmウエハー対応製造ラインを導入へ

東芝デバイス&ストレージは2021年3月10日、加賀東芝エレクトロニクス(以下、加賀東芝)構内に300mmウエハー対応の製造ラインを導入し、パワーデバイスの生産能力を増強すると発表した。同ラインは2023年度上期に稼働を開始する予定だ。投資金額は約250億円。