1000コアを搭載、RISC-VベースのAIアクセラレーター:EsperantoがHot Chips 33で発表(2/2 ページ)

新興企業Esperantoは、これまで開発の詳細を明らかにしてこなかったが、2021年8月22〜24日にオンラインで開催された「Hot Chips 33」において、業界最高性能を実現する商用RISC-Vチップとして、ハイパースケールデータセンター向けの1000コア搭載AI(人工知能)アクセラレーター「ET-SoC-1」を発表した。

低消費電力を追求したチップ設計

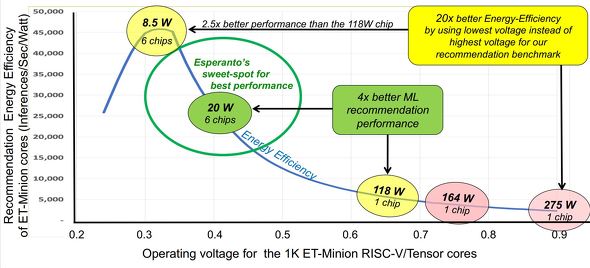

大電力を必要とするチップアクセラレーターを提供する競合他社とは異なり、Esperantoは複数接続できる低消費電力のチップを提供する。高価なHBM(High Bandwidth Memory)に頼ることなく、より多くのピンをメモリI/Oに使用できるため、メモリ帯域幅の要件に対応できる。

同社のハードウェアは、汎用コンピュータとしても設計されている。Ditzel氏は、「推奨モデル(recommendation model)に焦点を当てているが、当社のチップは並列処理を加速することができる。Glacier Pointには約6000個の並列コアが搭載されており、各コアは2つのスレッドを実行する」と説明する。

もう1つの特長は、積極的な省エネ設計だ。顧客の要求により電力バジェットは合計120Wに設定されていて、Glacier Pointカードの電力は最大120W(20W×6)である。これに対し、AI推論アクセラレーターは、その10倍以上の電力で動作する。

同社は、この問題に複数の方面からアプローチした。まず、クロック周波数を最適な1GHz程度まで下げたほか、電源電圧はSRAMの限界を超えた0.4V程度まで下げている。スイッチング容量は最小の命令セットを持つ無駄のないRISC-Vコアを使うことで改善し、トランジスタの数を減らすことができた。プロセス技術は、先進的でありながら安定したTSMCの7nmを採用している。

コアの設計

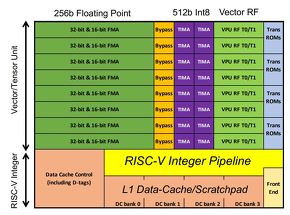

Esperantoのチップには、AIのワークロードを処理する1088個のET-Minionコアが搭載されている。コアは64ビットのインオーダーRISC-Vプロセッサで、Esperanto独自のAIに最適化されたベクトルとテンソルユニットがチップの大部分を占めている。浮動小数点のMACが構成の大半を占めており、珍しいことに、整数のMACは浮動小数点の2倍の処理幅を持っている(顧客の要求による)。

また、深層学習モデルでよく使われるシグモイド関数などのベクトル超越命令もサポートしている。コアは単一の低電圧ドメインで動作するため、多くのトランジスタを使用し、小型のL1キャッシュにSRAMを搭載することで、安定した性能を確保している。

各コアは1GHz当たり128GOPSの処理能力を有する。カスタムのマルチサイクルテンソル命令は、大規模な行列の乗算を別のコントローラーが引き継ぎ、512ビット幅をフルに使用し、最大512サイクル実行する。これにより、コントローラーが次のRISC-V命令をフェッチする前に、1つのテンソル命令で6万4000以上の演算を実行することができる。ワークロードの大部分がテンソル命令を使用するため、命令のバンド幅が減少。そのため、512クロックサイクル当たり1つの命令しか必要ない。

8つのET-Minionコアが物理的に近いことを利用して、修正された命令が実行される。「Cooperative Load」と呼ばれる機能では、キャッシュを取得せずにコア間で直接データを転送することができ、省電力化を実現した。さらに、8つのコアが大容量のL2キャッシュを共有することで、エネルギー効率を高めている。

ET-SoC-1では、8コア×4で「Minion Shire」と呼ぶ領域を構成している。1つのチップに34のMinion Shireがあるので合計1088コア(8×4×34)となっている(Ditzel氏は、「歩留まり向上のため1024個のコアだけで計算することも可能」と説明する)。現在のアクセラレーターの構成ではなく、将来のスタンドアロン動作を想定して、Arm「Cortex-A72」とほぼ同等の性能を持つ4つのET-Maxionコアを搭載している。Minion Shireそれぞれに独立した電圧供給を行い、個々の電圧を微調整することで、閾値電圧の変動を緩和している。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

EdgeQ、「5G基地局オンチップ」のサンプル出荷を開始

EdgeQ、「5G基地局オンチップ」のサンプル出荷を開始

5Gの展開に向けBasestation-on-a-Chip(ベースステーションオンチップ)とソフトウェアを開発するスタートアップ企業であるEdgeQがサンプル出荷を開始した同チップとPHYソフトウェアの詳細について説明した。 RVVプロセッサで初めてASIL D Ready認証を取得

RVVプロセッサで初めてASIL D Ready認証を取得

RISC-V Vector Extension(RVV)を実装したエヌエスアイテクス製のDFP(Data Flow Processor)「DR1000C」が、SGS-TUVから「ISO 26262 ASIL D Ready」の認証を取得した。「RVVプロセッサでは初めての認証取得」だという。 RISC-V International CTOに聞く「課題や地政学的影響」

RISC-V International CTOに聞く「課題や地政学的影響」

RISC-Vコミュニティーメンバー組織であるRISC-V Internationalは2020年8月3日、旧組織であるRISC-V Foundationからの移行に伴い、スイスに拠点を置く新しい法人組織の取締役メンバーを16人任命したと発表した。RISC-V Internationalは2020年6月にも、Mark Himelstein氏のCTO(最高技術責任者)就任を発表している。米国EE Timesは同年7月に、同氏にオンラインインタビューを行い、同氏の担っている役割や、RISC-Vの幅広い普及実現に向けた課題、地政学的な影響などについて話を聞いた。 「第3期」を迎えた組み込みCPU、けん引役はRISC-Vか

「第3期」を迎えた組み込みCPU、けん引役はRISC-Vか

32/64ビットの組み込みプロセッサにおいて、“第1期”と“第2期”では、独自のアーキテクチャが基本だった。だが、“第3期”はそうではなさそうだ。第3期の主役は、業界標準でオープンスタンダードのアーキテクチャである。このムーブメントの先駆けとなったのがRISC-Vだ。 戦いの火ぶたが切られたエッジAI市場

戦いの火ぶたが切られたエッジAI市場

人工知能(AI)は過去2年間で、世界的なメガトレンドへと変化した。機械学習は、消費者や自動車、産業、エレクトロニクス全般など、ほぼ全てに何らかの形で影響をもたらしている。さらに、私たちがまだ、うかがい知れない方法で社会や生活に影響を与えると思われる。 RISC-V上にオープンなセキュリティ基盤構築へ

RISC-V上にオープンなセキュリティ基盤構築へ

セキュアオープンアーキテクチャ・エッジ基盤技術研究組合(TRASIO)は、オープンソースの命令セットアーキテクチャ(ISA)である「RISC-V」上に、オープンなセキュリティ基盤を構築するための研究開発に取り組む。