2層上下の配線層をダイレクトに接続する「スーパービア」の課題(前編):福田昭のデバイス通信(323) imecが語る3nm以降のCMOS技術(26)(2/2 ページ)

今回から、スーパービアが抱える本質的な課題と、その解決策を前後編の2回に分けて解説する。

ブロックする配線の本数が多層配線のレイアウトを左右

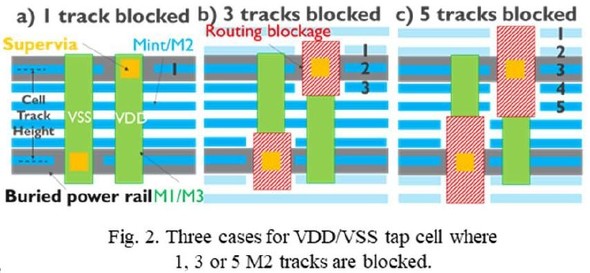

1個のスーパービアが何トラック(何本)のM2をブロックするか。最も少ないのは1トラックだ。ただしimecが3nm世代で想定する多層配線の寸法は、M1とM3が36nmピッチ、M2が21nmピッチである。最短ピッチのM2を、スーパービアでブロックする。1トラックのブロックではM2のレイアウトに与える影響は少ないものの、スーパービアとM2の絶縁を維持できるかが懸念される。

セルの高さが5トラック(5T)のスタンダードセルにおける、「スーパービア(supervia)」と第2層金属配線(M2)のレイアウト。スーパービアがブロックするM2のトラック数を変更して図示している。左(a)は1トラック、中央(b)は3トラック、右(c)は5トラックの場合。出典:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5)) (クリックで拡大)

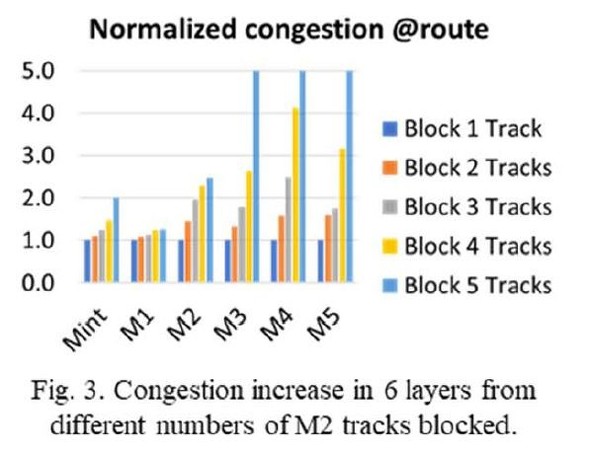

始めはブロックするトラックの数を増やしたときの影響を検討しよう。ブロックするトラック数が多すぎると、M2のレイアウトが阻害される。その影響は第3層から上層の金属配線層をレイアウトするときに、配線混雑度の上昇となって現れる。imecはブロックされるM2の数を1トラックから5トラックまで変えて第0層(Mint)から第5層(M5)の配線混雑度を推定した。1トラックのブロックによる混雑度を基準値「1」とすると、3トラックまでは混雑度はあまり増加しないものの、4トラックと5トラックでは第3層(M3)から第5層(M5)の混雑度が急激に上昇する。

スーパービアがブロックするM2のトラック数と、M0(Mint)からM5の配線混雑度の関係。ブロックするトラック数が3トラックを超えると、M3とM4、M5の配線混雑度が急激に増大する。なお混雑度は、ブロックするM2のトラック数が最も少ない(1トラックの)場合を基準とした相対値。出典:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5)) (クリックで拡大)

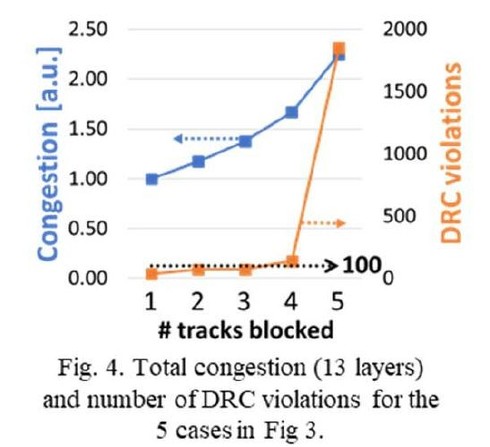

さらに、ブロックするトラック数が多すぎるとレイアウト設計が困難になる。多層配線のレイアウト設計(配置配線(PnR)工程)で使用する設計ツールには、レイアウトが設計ルールに違反していないかどうかを検出する機能(設計ルールチェック(DRC))が組み込まれている。スーパービアがブロックするM2のトラック数が増えると、配線の混雑度が上昇するとともに、DRC違反の数が増加する。13層の多層配線構造を想定したときの推定では、ブロックされるM2が5トラックに達すると、DRC違反の数は1500を超える。一方でブロックされるM2が4トラック以下の場合は、DRC違反は100前後に収まる。

ブロックするM2のトラック数と、配線混雑度(左の縦軸)およびDRC違反数(右の縦軸)の関係。4トラックまではDRC違反は100前後にとどまる。5トラックになるとDRC違反は急激に増加し、1500を超える。13層の多層配線構造を想定したときの推定値。出典:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5)) (クリックで拡大)

(後編に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

多層配線のビア抵抗を大幅に低減する「スーパービア」

多層配線のビア抵抗を大幅に低減する「スーパービア」

今回は、奇数番号(あるいは偶数番号)で隣接する配線層(2層上あるいは2層下の配線層)を接続するビア電極の抵抗を大幅に下げる技術、「スーパービア(supervia)」について解説する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。