MRAMの制約を克服するスピン軌道トルク:SOT-MRAM開発スタートアップ

AntaiosのCEO(最高経営責任者)を務めるJean-Pierre Nozières氏は米国EE Timesのインタビューで、「スピン軌道トルク(SOT)MRAMは、スピン伝達トルク(STT)MRAMが現在直面している“トリレンマ”に対処できる」と語った。

STT-MRAMの“トリレンマ”を克服

次世代の組み込みMRAM(磁気抵抗RAM)は、レシピの材料を入れる順番を変えるだけでできるかもしれない。

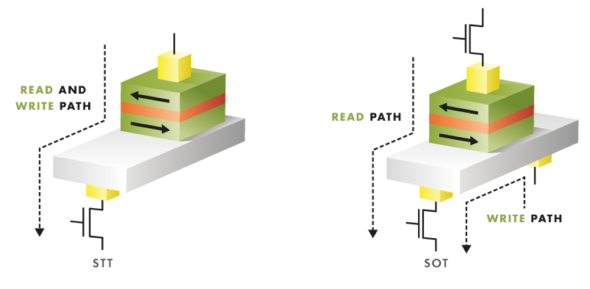

AntaiosのCEO(最高経営責任者)を務めるJean-Pierre Nozières氏は米国EE Timesのインタビューで、「スピン軌道トルク(SOT)MRAMは、スピン伝達トルク(STT)MRAMが現在直面している“トリレンマ(三者択一の状況または三重苦)”に対処できる」と語った。STT-MRAMは書き込み時にデバイスのトンネル酸化物に大きな電圧がかかるため、データ保持や書き込みの耐久性、書き込み速度との間で継続的にトレードオフが発生する。つまり、STT-MRAMはほぼ成熟しているにもかかわらず、高速性と無限の耐久性、十分なデータ保持のコンビネーションが必要となる高速RAMアプリケーションの要件を満たすには、依然として制約があるということだ。

Antaiosは2017年に設立され、2019年にスピントロニクス効果の1つであるSOTを利用して、第3世代のMRAMの開発を強化し始めた。Nozières氏は、「SOTは、製造プロセスを大きく変更せずに、STT-MRAMおよびその他の前世代のテクノロジーの制約を克服できると期待されている」と述べている。SOT-MRAMは、書き込み中にデバイスのトンネル酸化膜にかかる高電圧を完全に排除することでトリレンマを解決し、無制限の耐久性を実現するという。同氏は、「現在の技術は、組み込みフラッシュメモリをSTT-MRAMに置き換えることに限定されているため、データ保持力、速度、耐久性の間にトリレンマがある。この制約を取り除くことで、前世代では対処できなかった高速アプリケーションに現在使われているフラッシュメモリやSRAMなどのメモリを置き換えられる可能性がある」と述べている。

もう1つのSOT-MRAM固有の利点は、データ保持のリーク電流がなく、電離放射線によるデータ妨害の影響を受けないことだという。これらは両方とも、SRAMの深刻な問題である。SOT-MRAMは書き込みが非常に高速であるため、STT-MRAMと比べて書き込みエネルギーを削減できるという利点もある。同氏は、「これによって、システムレベルの性能が大きく向上する」と述べている。

期待される使用例は

SOT-MRAMの初期の適用事例の1つに、CPUのラストレベルキャッシュ(LLC)がある。LLCは、従来の組み込みアーキテクチャの一部として、もしくは、非常に大きなキャッシュを持つハイエンドCPU向けに、異なるプロセスのさまざまなウエハーの“ダイ・オン・ダイ”を強化する3Dアセンブリ代替技術として使用される。Nozières氏によると、どちらも、現在開発中のSOT-MRAMのプロセスフローと完全に互換性があるという。

SOT-MRAMのもう1つの有望な使用例は、エッジデバイスの人工知能(AI)、いわゆるエッジAIだ。エッジAIのほとんどは、フォンノイマン型アーキテクチャで動作し、大量の外部メモリを使用する。オンチップSOT-MRAMは、消費電力を大幅に削減しながら、速度と耐久性が重要となるキャッシュ/ワーキングメモリのように動作できるという。

SOT-MRAMのメリットは、マイクロコントローラーアーキテクチャにも適用できる。現在、フラッシュメモリのブロックとSRAMブロックが別々のアーキテクチャになっているが、これは本棚の本を追加するために常に入れ替えているようなものだ。Nozières氏は、「本棚の本を入れ替えているだけなので、多くの時間とエネルギーを必要とする。それがマイコンの中で起きていることだ」と説明する。SOT-MRAMは、組み込みフラッシュメモリのようなデータ保持と、メインメモリの読み書きサイクルタイムを10ナノ秒以上の速さで同時に実現できるため、電力、性能、コストを大幅に改善した単一の“XIP(eXecute-In-Place)”ブロックが可能になる。

SOTは、現在のSTT-MRAMと同様に、スピン転移効果に基づいている。ただし、電流をスピン偏極させるための磁性層は必要なく、スピンの供給源は、スピン軌道相互作用を介したSOT層材料の格子のみである[クリックで拡大] 出所:Antaios

Nozières氏は、「SOT-MRAMにはまだ長い道のりがある」と語る。しかし、Antaiosのアプローチは、全てを自社で行うのではなく、製造側を含めた関係を築くことだ。同社は2020年、フランスのベンチャーキャピタルInnovacomとSofimac Innovationを中心に、シリコンバレーに拠点を置くApplied MaterialsのベンチャーキャピタルApplied Venturesを加えた3社から投資を受けた。Nozières氏は、Antaiosが「MRAMを取り巻くエコシステムを活用しようとしている」と述べた。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

次世代メモリ市場、2031年までに440億米ドル規模へ

次世代メモリ市場、2031年までに440億米ドル規模へ

米国の半導体市場調査会社であるObjective AnalysisとCoughlin Associatesは、共同執筆した年次レポートの中で「次世代メモリが、さらなる急成長を遂げようとしている」という見解を示した。次世代メモリ市場は2031年までに、440億米ドル規模に達する見込みだという。 産総研、MRAMの磁気安定性を飛躍的に改善

産総研、MRAMの磁気安定性を飛躍的に改善

産業技術総合研究所(産総研)は、原子層レベルで制御されたタンタル(Ta)を下地に用いることで、磁気抵抗メモリ(MRAM)の磁気安定性を飛躍的に改善する技術を開発した。 産総研、TMR素子の記憶安定性を約2倍に向上

産総研、TMR素子の記憶安定性を約2倍に向上

産業技術総合研究所(産総研)の薬師寺啓氏は、スピントルク書込型磁気ランダムアクセスメモリ(STT-MRAM)に用いられる垂直磁化トンネル磁気抵抗(TMR)素子の記憶安定性を従来の2倍に向上させることに成功した。素子サイズが20nm以下の大容量SST-MRAMを実現することが可能となる。 MRAM用単結晶MTJ素子を300mmウエハー上に作製

MRAM用単結晶MTJ素子を300mmウエハー上に作製

産業技術総合研究所(産総研)は、MRAM用の単結晶MTJ(磁気トンネル接合)素子をシリコンLSIに集積化するための3次元積層プロセス技術を開発した。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 次世代半導体メモリの開発ロードマップ

次世代半導体メモリの開発ロードマップ

今回から、「次世代メモリ(Emerging Memory)」の講演部分を紹介する。