10年で5世代の進化を遂げた高性能パッケージング技術「CoWoS」(後編):福田昭のデバイス通信(335) TSMCが開発してきた最先端パッケージング技術(8)

前編に続き、「CoWoS(Chip on Wafer on Substrate、コワース)」の進化について解説する。

(ご注意)今回は前編の続きです。まず前編を読まれることを推奨します。

搭載するロジックとメモリの両方が常に大規模化

前編では、高性能パッケージング技術「CoWoS(Chip on Wafer on Substrate、コワース)」が最初の開発から約10年の間に派生品を生み出したこと、派生品を含めて3種類の「CoWoS」技術が存在することを説明した。さらに、「CoWoS」技術が2011年に初めて開発されてから、どのように発展してきたかを振り返った。

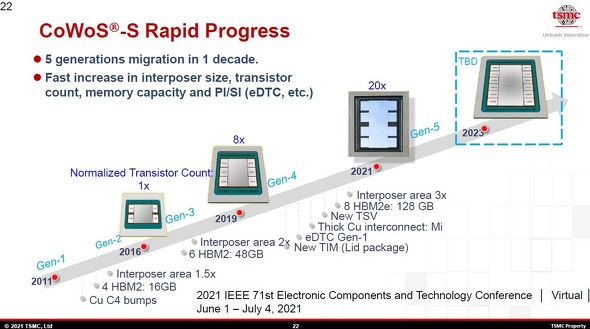

オリジナルの「CoWoS」技術は中間基板(インターポーザ)にシリコン(Si)基板を使う。現在ではこのタイプを「CoWoS_S(Silicon Interposer)」とTSMCは呼称している。前編で説明したように、2011年の第1世代から2019年の第4世代までの間に、「CoWoS_S」(従来の「CoWoS」)技術はインターポーザ面積とトランジスタ数、メモリ容量の拡大を継続してきた。

「CoWoS_S」(従来の「CoWoS」)の進化。2011年の第1世代から、2021年の第5世代まで改良を重ねた。2023年には次世代の「CoWoS_S」を開発する[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

インターポーザはもともとから巨大だったのが、さらに巨大化した。第1世代がレチクル1枚に相当する面積(775mm2)であり、第2世代と第3世代ではレチクル1.5枚に相当する面積(1150mm2と1170mm2)に広がった。第4世代だとさらに大きくなり、レチクル2枚に相当する面積(1700mm2)に達した。

インターポーザに搭載するシリコンダイは、当初は複数のロジックダイだった。第3世代からはロジックとメモリの混載に対応した。ロジック(SoC)ダイと高速DRAMモジュール「HBM(High Bandwidth Memory)」の積層ダイ群を搭載するようになった。具体的には、1枚のSoCダイと4個のHBM(4Gバイト×4個で合計16Gバイト)を混載した。第4世代ではSoCダイの面積(集積規模)が拡大するとともに、混載するHBMが6個に増えた。1個のHBMに記憶可能な容量が2倍に増えたことにより、HBMの総容量は第3世代の3倍(48Gバイト)と大きく増加した。

「CoWoS_S」の改良がHPCシステムの進化を後押し

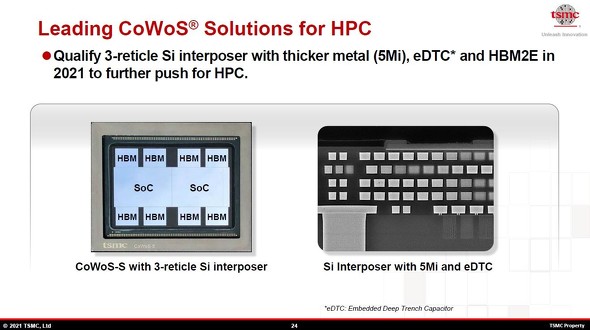

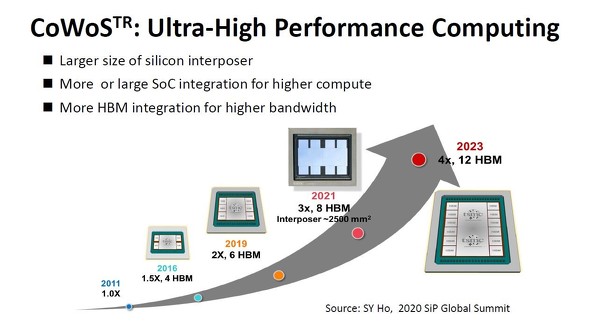

ことし(2021年)に開発した第5世代の「CoWoS_S」(従来の「CoWoS」)は、Siインターポーザをレチクル3枚に相当する2500mm2とさらに拡大するとともに、第3世代の2倍である8個のHBMを搭載する。ロジックのシリコンダイは再びチップレットとなり、2個のミニダイを総計1200mm2の領域に載せる。搭載可能なHBMの仕様は「HBM2E」(HBM第2世代の強化版)である。

Siインターポーザの再配線層(RDL)は、銅(Cu)配線を従来よりも厚くすることでシート抵抗を半分以下に低減した。5層のCu配線によってシリコンダイ間を接続する。またシリコン貫通ビア(TSV)による高周波損失を低減するため、TSVを再設計した。2GHz〜14GHzの高周波領域における挿入損失(S21)は、従来の0.1dB強から再設計後は0.05dB強に減少した。さらに、深い溝による高容量のキャパシタ「eDTC(embedded Deep Trench Capacitor)」をSiインターポーザに作り込むことにより、電源系を安定化した。eDTCの容量密度は300nF/mm2である。電源分配ネットワーク(PDN)のインピーダンスは、100MHz〜2GHzの周波数領域でeDTCによって従来の35%以下に減少した。

第5世代の「CoWoS_S」(従来の「CoWoS」)を支える要素技術[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

次世代(第6世代)の「CoWoS_S」は、2023年に開発する予定だ。Siインターポーザの大きさはレチクル4枚分とさらに巨大になる。単純計算では約3400mm2(約58.6mm角)に達する。ロジック部分はチップレットによる2枚以上のミニダイを搭載し、メモリ部分は12個のHBMを載せる。対応するHBMの仕様は、「HBM3」となるもようだ。

「CoWoS_S」(従来の「CoWoS」)の開発ロードマップ[クリックで拡大] 出所:TSMC(2020年12月に開催された国際学会IEDMのショートコース「Advanced 3D System Integration Technologies」のスライドから)

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

「InFO」技術を改良した2種類のパッケージのうち、ウエハー規模の巨大なパッケージング技術「InFO_SoW」を解説する。 モバイル向け小型薄型パッケージ「InFO」が進化

モバイル向け小型薄型パッケージ「InFO」が進化

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。 「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。