連載

キオクシアの四半期業績、売上高が過去最高を記録:福田昭のストレージ通信(207)(2/2 ページ)

今回は、キオクシアの2021会計年度第2四半期(2021年7月〜9月期)の業績を紹介する。

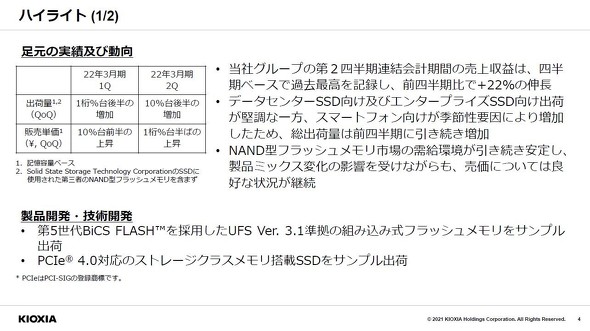

ビット換算の出荷量は前四半期比で10%台後半と大きく増加

NANDフラッシュメモリのビット換算出荷量と販売単価(記憶容量当たりの単価)の相対的な推移(前四半期との比較)は、いずれも前四半期と同様に増加傾向が続く。ビット換算出荷量は10%台後半の増加、販売単価は1桁%台半ばの上昇である。

製品開発のハイライトではまず、2021年8月11日にUFS(Universal Flash Storage)バージョン3.1準拠のフラッシュメモリのサンプル出荷を始めたと発表した(参考記事:「キオクシア、UFS Ver3.1準拠のフラッシュメモリ)。第5世代の3D NANDフラッシュ技術「BiCS5」(112層の3次元メモリセル技術)で製造したNANDフラッシュメモリを搭載する。記憶容量が256Gバイトの品種と512Gバイトの品種を用意した。

また2021年9月14日には、高速3D NAND技術「XL-FLASH」で製造した高速NANDフラッシュと既存の3D NAND技術「BiCS」で製造した高密度NANDフラッシュを搭載したエンタープライズ/データセンター向け高速SSD「FL6」のサンプル出荷を始めたと発表した(リリース)。インタフェースはPCIe 4.0およびNVMe 1.4のデュアルポート。記憶容量は800Gバイト〜3.2Tバイトである。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

モバイル向け小型薄型パッケージ「InFO」が進化

モバイル向け小型薄型パッケージ「InFO」が進化

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 東京工大ら、SOT-MRAM素子の原理動作実証に成功

東京工大ら、SOT-MRAM素子の原理動作実証に成功

東京工業大学と米国カリフォルニア大学ロサンゼルス校を中心とした国際研究チームは、トポロジカル絶縁体と磁気トンネル接合(MTJ)を集積したスピン軌道トルク磁気抵抗メモリ(SOT-MRAM)素子を試作し、読み出しと書き込みの原理動作を実証した。 チップレットと3次元集積が「ムーアの法則」を牽引

チップレットと3次元集積が「ムーアの法則」を牽引

今回から、2021年8月にオンラインで開催された「Hot Chips」の技術講座より、「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」の講演内容を紹介する。 PCMの課題解決、フレキシブル基板が鍵になる可能性

PCMの課題解決、フレキシブル基板が鍵になる可能性

超格子材料とフレキシブル基板を組み合わせれば、相変化メモリPCM(Phase Change Memory)の主要な欠点の1つを解決できる可能性がある。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。