省電力の高速CPUにつながる? 「CasFET」技術:新たなスイッチング手法を適用

米国パデュー大学の研究チームは、より小型で高密度、低電圧、低消費電力の次世代トランジスタにつながる可能性のある技術を発表した。この研究成果によって、より少ない電力でより多くの演算を行う、高速CPUが実現するかもしれない。バデュー大学が「CasFET(Cascade Field-Effect Transistor)」と呼ぶこの技術は、半導体のスケーリングの課題と最先端の半導体設計の製造コストの高騰に対処すると期待されている。

米国パデュー大学(Purdue University)の研究チームは、より小型で高密度、低電圧、低消費電力の次世代トランジスタにつながる可能性のある技術を発表した。この研究成果によって、より少ない電力でより多くの演算を行う、高速CPUが実現するかもしれない。バデュー大学が「CasFET(Cascade Field-Effect Transistor)」と呼ぶこの技術は、半導体のスケーリングの課題と最先端の半導体設計の製造コストの高騰に対処すると期待されている。

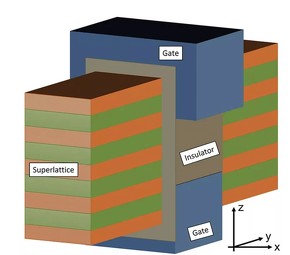

CasFET(Cascade Field Effect Transistor)は、小型/低消費電力で、オン/オフの切り替えに必要な印加電圧が少ない、より高性能なCPUの設計に役立つ可能性がある[クリックで拡大] 出所:パデュー大学

課題の中には、十分に高いオン電流とより低いオフ電流が必要なナノトランジスタの性能要件を満たすことや、オン/オフ切り替え時のわずかな差に対応することなどがある。

これらは、トランジスタの微細化を遅らせてきた問題の1つで、Intelが最近10nmから7nmプロセスへ移行した際に注目を集めた。

CasFETは、これらの問題を軽減し、高密度で低消費電力のトランジスタをより簡単に製造できるようにする技術とされている。同技術は、トランジスタの輸送方向に垂直な超格子構造を特徴とし、従来のFETデバイスとは違い、量子カスケードレーザーのように動作する。

パデュー大学のエンジニアらは、これまでに約150時間を費やしてCasFET技術の進展させるために使用するシミュレーションエンジンの開発に取り組んできた。

パデュー大学で電気工学およびコンピュータ工学の助教を務めるTillmann Kubis氏は、「大規模なナノテクノロジーと量子輸送のシミュレーションエンジンの開発に取り組んできたわれわれのチームは、大手ハイテク企業から高い支持を得ている」と述べている。

Kubis氏はさらに、「われわれは日々、トランジスタのあらゆる量子輸送を素粒子分解でモデル化することで、多くのトランジスタ技術と最新課題に触れている」と付け加えた。

同氏は博士課程の一環として、量子カスケードレーザーのモデリングにも取り組んだという。同氏は、「これらのレーザーは、外部電界によって、輸送特性がコヒーレント/バリスティックからステップワイズ/フォノン誘起トンネリングに切り替わる。われわれは、FETの標準的な電界効果スイッチングにこのスイッチング効果を追加した」と説明している。

同氏は、「スイッチング効果を追加したことで、最先端のトランジスタよりもゲートに対する感度がはるかに高いナノトランジスタが実現した。これは、GAA(Gate All Around)FETにも当てはまる。これらのトランジスタは全て、単一のスイッチングメカニズムに依存しているのに対し、われわれが開発したトランジスタには2つのスイッチングメカニズムがある」と付け加えた。

Kubis氏のチームは現在、CasFETデバイスのプロトタイプを設計中だという。同氏は、「この新しいスイッチング手法が効果的に機能すると確信している」と述べている。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intelがプロセスの名称を変更、「nm」から脱却へ

Intelがプロセスの名称を変更、「nm」から脱却へ

Intelは2021年7月26日(米国時間)、半導体プロセスとパッケージング技術の最新情報を説明するウェブキャスト「Intel Accelerated」を開催した。これを受けて、同社の日本法人インテルは7月28日に、Intel Acceleratedの内容を日本のメディア向けに説明するオンライン説明会を実施。インテル 執行役員常務 技術本部本部長である土岐 英秋氏が説明した。 IBMが「2nm」プロセスのナノシートトランジスタを公開

IBMが「2nm」プロセスのナノシートトランジスタを公開

IBMは、米国ニューヨーク州アルバニーにある研究開発施設で製造した「世界初」(同社)となる2nmプロセスを適用したチップを発表した。同チップは、IBMのナノシート技術で構築したGAA(Gate-All-Around)トランジスタを搭載している。 日台が連携、2nm世代に向けた「hCFET」を開発

日台が連携、2nm世代に向けた「hCFET」を開発

日本と台湾の国際共同研究グループは、2nm世代に向けた積層型Si/Ge異種チャネル相補型電界効果トランジスタ「hCFET」を開発した。 FinFETやGAAにも適用可能なエアスペーサー形成技術

FinFETやGAAにも適用可能なエアスペーサー形成技術

オンラインで開催された半導体デバイス/回路技術に関する国際会議「VLISシンポジウム 2020」(2020年6月15〜18日/ハワイ時間)で、IBM Researchの研究グループは先端CMOSにエアスペーサーを導入する技術を発表した。 Samsung、3nm「GAA FET」の量産を2021年内に開始か

Samsung、3nm「GAA FET」の量産を2021年内に開始か

Samsung Electronicsは、米国カリフォルニア州サンタクララで2018年5月22日(現地時間)に開催したファウンドリー技術の年次フォーラムで、FinFETの後継アーキテクチャとされるGAA(Gate All Around)トランジスタを2021年に3nmノードで量産する計画を発表した。 Samsung、2022年前半にGAA適用の3nmチップの生産開始

Samsung、2022年前半にGAA適用の3nmチップの生産開始

Samsung Electronicsファウンドリー部門は、2021年10月6〜8日にオンラインで開催した「Samsung Foundry Forum 2021」で、半導体プロセスのロードマップと製造工場の拡張について詳細を明らかにした。Samsungは、次世代のトランジスタ技術の開発を最も積極的に進めており、TSMCやIntelに先駆けて量産を開始する計画だ。