Samsung、MRAMベースのインメモリコンピューティングを発表:低消費電力AIチップ実現に向け

Samsung Electronicsは2022年1月13日(韓国時間)、磁気抵抗メモリ(MRAM)のイノベーションを発表した。同社は、「単一のメモリネットワーク内でデータストレージとデータコンピューティングの両方を実行できる、世界初のMRAMベースのインメモリコンピューティングを実現した。このMRAMアレイチップは、低消費電力AI(人工知能)チップの実現に向けた次なるステップだ」と主張している。

Samsung Electronicsは2022年1月13日(韓国時間)、磁気抵抗メモリ(MRAM)ベースのインメモリコンピューティングのデモを発表した。同社は、「単一のメモリネットワーク内でデータストレージとデータコンピューティングの両方を実行できる、MRAMベースのインメモリコンピューティングを実現した。このMRAMアレイチップは、低消費電力AI(人工知能)チップの実現に向けた次なるステップだ」と主張している。

インメモリコンピューティングアーキテクチャの利用が年々増加しているのは、エッジでデータを処理できるためで、これによってデータの移動量やネットワークの遅延を削減することができる。ただし、MRAMは抵抗が低いため、標準的なインメモリアーキテクチャで使用した場合、消費電力を削減する能力が制限されてしまう。そこで、Samsungはこの課題を解消できるインメモリコンピューティングの実現に取り組んできた。

SamsungのMRAMアレイチップは、「抵抗合算(resistance sum)」方式のインメモリコンピューティングアーキテクチャを適用して、この問題を解消するという。

Samsungによると、インメモリコンピューティングアーキテクチャは、従来、不揮発性メモリのクロスバーアレイに依存しており、アナログ方式で積和演算を実行している。だが、STT-MRAM(スピン注入磁化反転型磁気メモリ)のクロスバーアレイを作成するには課題が残る。

SamsungはNature誌に発表した論文の中で、「MRAMには、耐久性があることや大規模な商用化が可能であることなど、実用的なメリットがある。問題は、MRAMの抵抗値が低いために、アナログの積和演算で電流を合算する従来のクロスバーアレイでは消費電力が大きくなってしまうことだ」と述べている。

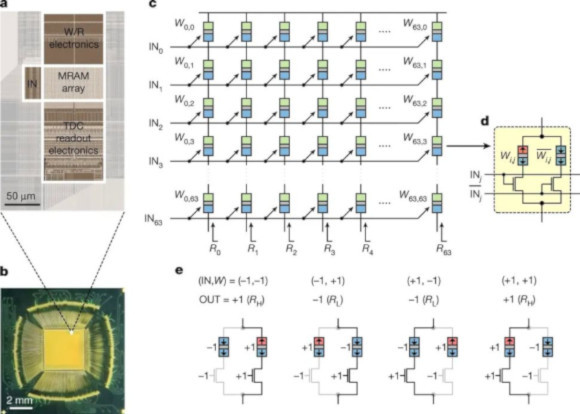

同論文によると、Samsungの研究チームは、MRAMセルをベースにした64×64のクロスバーアレイ構造のMRAMアレイチップの開発に成功し、アナログの積和演算に抵抗合算を用いるアーキテクチャで低抵抗の問題を克服したという。

同社は、MRAMアレイチップと読み出し回路を28nmのCMOS技術で統合した。

Samsung Advanced Institute of Technology(SAIT)が同社のエレクトロニクスファウンドリー事業部門および半導体研究開発センターと共同で率いる研究チームは、「このMRAMチップをAIベースのいくつかのインスタンスでテストした」と述べている。Samsungによると、MRAMベースのインメモリコンピューティングチップは、手書きの数字の分類で98%、さまざまなシーンでの顔検出で93%の精度を達成したという。

Samsungは、インメモリコンピューティングだけでなく、生物学的ニューラルネットワークのユースケースにもMRAMアレイチップを拡張することを狙う。同社はニューロモーフィックエレクトロニクスの研究に照準を合わせ、最近では2021年9月26日にニューロモーフィックチップの展望をまとめた論文を発表した。この論文では、脳をメモリチップにリバースエンジニアリングするという同社の考え方が提示されており、これによりニューロモーフィックチップは基本的に「コピー&ペースト」の手法で人間の脳をエミュレートすることができるようになる、としている。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

エッジAI発展に重要な「インメモリコンピューティング」

エッジAI発展に重要な「インメモリコンピューティング」

欧州最大級の半導体国際学会「ESSCIRC-ESSDERC 2021」(2021年9月、オンライン開催)で、STMicroelectronics(以下、ST)のデジタル&スマート・パワー技術およびデジタル前工程製造を担当エグゼクティブバイスプレジデント、Joël Hartmann氏が講演。エッジAI(人工知能)の展望を語る中で、「インメモリコンピューティングへの移行」の重要性を訴えた。 “脳型プロセッサ”を統合したイメージセンサー開発へ

“脳型プロセッサ”を統合したイメージセンサー開発へ

SynSenseとPropheseeは、Propheseeのイメージセンサー「Metavision」とSynsenseのニューロモーフィックプロセッサ「DYNAP-CNN」を統合したイベントベースの単一チップイメージセンサーを共同開発している。両社は今後、同イメージセンサーの設計、開発、製造、製品化でも連携し、小型化と安価を両立した超低電力センサーを生み出すことを目指す。 NeuroBlade、PIMを搭載した専用アプライアンスを発表

NeuroBlade、PIMを搭載した専用アプライアンスを発表

PIM(Processing-in-Memory)技術への関心は高まり続けている。イスラエル・テルアビブに拠点を置く新興企業NeuroBladeが、データアクセラレーターの出荷を開始したと発表した。同社のCEO(最高経営責任者)であるElad Sity氏は、「メモリ内部の処理機能を統合することにより、データの移動と、それによって生じるボトルネックを軽減することが可能だ」と述べている。 「PIMの可能性を広げる」、Samsung

「PIMの可能性を広げる」、Samsung

Samsung Electronics(以下、Samsung)は、PIM(Processing-in-Memory)を主流派の技術へと推進していく上で、新たなステップの実現を発表した。同社は2021年初めに、PIM技術を他の種類のメモリに統合するという構想の一環として、業界で初めて、PIM対応のHBM(High Bandwidth Memory)である「HBM-PIM」を、商用化されたアクセラレーターシステムに統合することに成功している。 Rain NeuromorphicsがアナログAIのデモチップをテープアウト

Rain NeuromorphicsがアナログAIのデモチップをテープアウト

Rain Neuromorphicsが、脳型アナログアーキテクチャのデモチップをテープアウトした。ランダムに接続されたメモリスタの3Dアレイを用い、ニューラルネットワークトレーニング/推論などを超低消費電力で計算することが可能だという。 組み込みAIを加速する、ルネサスの新Processing-in-Memory

組み込みAIを加速する、ルネサスの新Processing-in-Memory

ルネサス エレクトロニクスは、メモリ回路内でメモリデータの読み出し中に積和演算を行う既存のProcessing-in-Memory(PIM)を改良した、新たなPIM技術を開発したと発表した。同技術をベースに開発したAIアクセラレーターをテストチップに実装して推論処理を行ったところ、8.8TOPS/Wの電力効率を実証したという。