低損失の高速光電変換ユニット「COUPE」の概念:福田昭のデバイス通信(344) TSMCが開発してきた最先端パッケージング技術(17)

今回は電気信号を光信号に変換(あるいは電気信号を光信号に変換)する回路ユニット「フォトニックエンジン(PE:Photonic Engine)」の構成と、TSMCが考えるPEの実現手法「COUPE(COmpact Universal Photonic Engine)」の概念を説明する。

光伝送の送信側と受信側で同一の光電変換ユニットを使用

高性能プロセッサとその関連技術に関する国際学会「Hot Chips」が昨年(2021年)8月22日〜24日にオンラインで開催された。「Hot Chips」は高性能プロセッサの最新技術情報を入手できる貴重な機会として知られている。会期は3日間で、初日が「チュートリアル(Tutorials)」と呼ぶ技術講座、2日目と3日目が「カンファレンス(Conference)」と呼ぶ技術講演会となっており、講演会とは別にポスター発表の機会も用意される。オンライン開催となった昨年は、あらかじめ録画されたビデオをプログラムに沿って公開する形式となった。参加登録者は開催後も一定の期間は、オンデマンドで講演を聴講できる。

初日の「チュートリアル(Tutorials)」では、13件の講演が実施された。その中で「先進パッケージング技術」に関する講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」が極めて興味深かった。講演者はTSMCで研究開発担当バイスプレジデント(現在はシステム集積化手法開発担当バイスプレジデント)をつとめるDouglas Yu氏である。

そこで本講演の概要を第328回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン。前回から、最後のテーマである「Si Photonics Integration(COUPE)」の講演部分を紹介する[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

前回から、最後のパートである「シリコンフォトニクス」に関する講演部分を紹介している。前回は銅ケーブル(銅配線)伝送と光伝送の境界(伝送速度×距離)を定義するとともに、シリコンフォトニクスを実装する手段の変遷を解説した。今回は電気信号を光信号に変換(あるいは電気信号を光信号に変換)する回路ユニット「フォトニックエンジン(PE:Photonic Engine)」の構成と、TSMCが考えるPEの実現手法「COUPE(COmpact Universal Photonic Engine)」の概念を説明する。

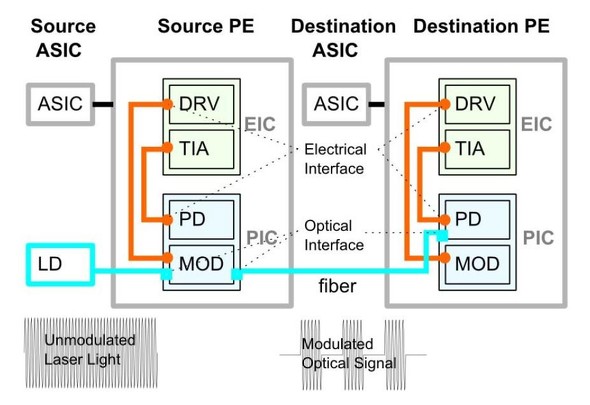

半導体ロジックのASICが入出力する高速な電気信号を光信号に変換する(あるいは光信号を電気信号に変換する)「フォトニックエンジン(PE)」の基本的なアーキテクチャは、光伝送の送信側と受信側で変わらない。大まかには、電気回路部(EIC:Electrical IC)と光回路部(PIC:Photonic IC)で構成する。EICは光変調の駆動回路(DRV)とインピーダンス変換アンプ(TIA:transimpedance amplifier)を内蔵する。PICは光検出器(PD:photodetector)と光変調回路(MOD)を備える。

送信側のPEには半導体レーザー(LD:laser diode)と光ファイバ(半導体レーザー用と信号伝送用)を外付けする。半導体レーザーから出た光は、光ファイバ(半導体レーザー用)を介してPICの光変調回路(MOD)に至る。MODによって変調された光信号は、光ファイバ(信号伝送用)を通して受信側へと送出される。

フォトニックエンジン(PE)を利用した光ファイバ伝送の仕組み。出所:TSMC(ECTC2021の発表論文「Heterogeneous Integration of a Compact Universal Photonic Engine for Silicon Photonics Applications in HPC」から)

受信側のPEには光ファイバ(信号伝送用)を外付けする。光ファイバで伝送された光信号は、光検出器(PD)によって電流信号に変換される。電流信号はインピーダンス変換アンプ(TIA)によって電圧信号に変わる。

モノリシック集積とハイブリッド集積の利害得失

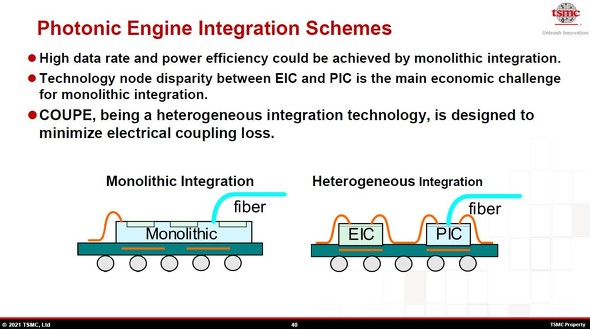

フォトニックエンジン(PE)の実現手法としては、モノリシック集積とハイブリッド集積(ヘテロジニアス集積)の2つが考えられる。EICとPICの電気的な接続の損失を最も少なくし、高速動作と低消費電力動作を両立しやすいのはモノリシック集積である。ただしPICとEICには半導体製造技術に大きな格差がある。PICは加工寸法の長いプロセスを使うので、EICが高密度にならない。

フォトニックエンジン(PE)の実現手法。左図はモノリシック集積、右図はハイブリッド集積(ヘテロジニアス集積)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

ハイブリッド集積(ヘテロジニアス集積)だとEICとPICが別の半導体チップとなるので、EICには加工寸法の短い最先端のプロセスを使える。ただしEICとPICの電気的な接続による損失は、モノリシック集積に比べて大きくなる。例えばEICチップとPICチップを3次元積層(3D Stack)することで、電気信号の接続損失を小さくする。

TSMCは、電気的な接続による損失が非常に少ないハイブリッド集積(ヘテロジニアス集積)技術を開発し、「COUPE(COmpact Universal Photonic Engine)」と呼称している。技術の詳細は明らかにしていない。

7nmのFinFET技術と、マイクロリング変調器(MRM:Micro-Ring Modulator)によるNRZ(Non-Return-Zero)符号のPAM4変調信号を112Gビット/秒の速度で送信するフォトニックエンジン(PE)で、消費電流を比較した。従来の3次元積層PEに比べ、COUPEの消費電流は6割に抑えられたとする。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

シリコンフォトニクスとは何か

シリコンフォトニクスとは何か

今回は、「シリコンフォトニクス」技術を紹介する。そもそも「シリコンフォトニクス」とは何か、そしてその利点と課題について解説したい。 シリコンフォトニクスの技術開発ロードマップ

シリコンフォトニクスの技術開発ロードマップ

今回は、シリコンフォトニクスの技術開発ロードマップを解説する。シリコンフォトニクスの性能向上とコストを、16/14nmから5nm、3nmの技術ノードに沿って見ていこう。 光トランシーバーForm Factorの新動向(1) 〜“Beyond 400G”の議論が活発に

光トランシーバーForm Factorの新動向(1) 〜“Beyond 400G”の議論が活発に

今回は、“Beyond 400G”に向けた議論とともに、Pluggableにおける3つの問題点を紹介する。 シリコンフォトニクスデバイスの試作体制を構築

シリコンフォトニクスデバイスの試作体制を構築

産業技術総合研究所(産総研)電子光技術研究部門とTIA推進センターは、シリコンフォトニクスデバイスの試作体制を構築した。国内外の民間企業や大学もこれらの設計製造環境を利用することができる。 NEDOら、オンボード光モジュールで400Gbps実現

NEDOら、オンボード光モジュールで400Gbps実現

新エネルギー・産業技術総合開発機構(NEDO)と光電子融合基盤技術研究所(PETRA)は、外形寸法が34×36×8mmと極めて小さいオンボード光モジュールを用いて、400Gビット/秒(bps)の伝送速度を実現した。