「ムーアの法則」減速への打開策? ヘテロジニアス設計:PPACの改善を加速(2/2 ページ)

半導体業界では現在、IoT(モノのインターネット)やビッグデータ、AI(人工知能)などによる新しい成長の波が押し寄せている。しかし、半導体イノベーションの必要性がこれまで以上に高まっているにもかかわらず、従来型のムーアの法則の2D(2次元)微細化は、減速の一途にある。

ハイブリッドボンディング

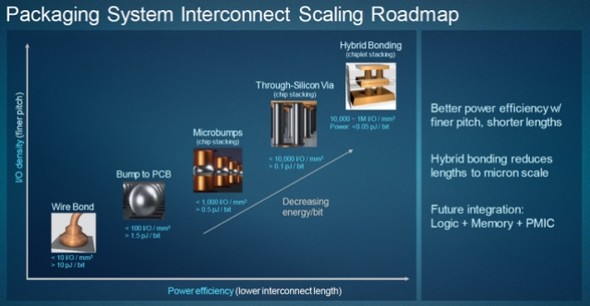

高性能パッケージング分野の次なる革新となるのが、ハイブリッドボンディングだ。既存のマルチチップパッケージング技術を大幅に進化させ、金属バンプを使ってI/Oピンを基板に接続し、基板の配線を使用してチップ間の電気相互接続を確立する。ハイブリッドボンディングは、半導体チップとウエハーをCu-Cu接合(copper-to-copper bonding)で直接接続することにより、配線距離を短縮し、I/O密度を高め、電力効率やシステム性能を向上させることが可能だ。TSVと比べると、I/O密度を10倍に、1ビット当たりのエネルギーを2倍に、それぞれ高められる。

ハイブリッドボンディングを実現するためには、幅広い種類の高度な半導体製造技術が必要である。最高性能を達成するには、ボンディングパッド形成や平たん化、表面処理、ボンディングなど向けの主要技術を最適化することが不可欠だ。

大手の半導体メーカー/システムメーカーにとっては今後、ヘテロジニアス設計や、ハイブリッドボンディングのような高性能パッケージング技術の重要性がますます高まっていくだろう。Applied Materialsは、深く幅広いポートフォリオを取りそろえることにより、こうした傾向を加速させるためのサポートを提供している。また、当社がシンガポールに置く高性能パッケージングの研究施設では、ダイツーウエハー(die-to-wafer)およびウエハーツーウエハー(wafer-to-wafer)のハイブリッドボンディングに向けた完全な製造技術を実証すべく、顧客企業や業界パートナーと協業しながら取り組みを進めている。高性能パッケージングエコシステムを構築し、顧客企業のPPACtロードマップを加速させることで、減速するムーアの法則の微細化の課題を打開していきたいと考えている。

パッケージングとローカライゼーション

新型コロナウイルス感染症(COVID-19)のパンデミックによって引き起こされた部品の供給難は、さまざまな業界に経済的混乱をもたらした。中でも最も顕著な影響が及んだのが、自動車業界だ。メーカーだけでなく、国家全体で半導体調達戦略の見直しが進められる中、その影響はパッケージングにも及んでいる。

米国電子回路協会(IPC)と調査会社TechSearch Internationalが2021年11月に発表したレポートによると、高性能の半導体パッケージング生産量全体に占める北米の割合は、わずか3%にすぎないという。このような弱点は、米国議会が2021年に可決した、520億米ドル規模の刺激策から成る「CHIPS Act」法案によって対応されることになるだろう。同法案では、「National Advanced Packaging Manufacturing Program(国による高度パッケージング製造プログラム)」の設立が提唱されており、Applied Materialsをはじめ、米国半導体業界のリーダー企業がサポートを提供している。

【著者】

Nirmalya Maity氏は、Applied MaterialsのAdvanced Packagingでコーポレートバイスプレジデントを務める。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

CHIPS法成立に向け米政府とチップメーカーが取り組み強化

CHIPS法成立に向け米政府とチップメーカーが取り組み強化

米国政府と同国のチップメーカーは2022年4月4日(米国時間)の週、520億米ドル規模の刺激策から成る「CHIPS Act」を通過させるための取り組みをそれぞれ強化した。CHIPS Actは、現在そして将来の戦略的脆弱性を警告するものであり、現在、議会の承認を待っている状況にある。 システムトークス、設計リプレースサービスを開始

システムトークス、設計リプレースサービスを開始

システムトークスは、「設計リプレースサービス」事業を2022年4月15日より始めた。深刻化する半導体不足などの課題に対し、回路基板の修正変更などによって、これらを解決できるソリューションを提供する。 米半導体支援策、成功には組み立て/テスト強化が必須

米半導体支援策、成功には組み立て/テスト強化が必須

米国は現在、エレクトロニクス業界が全盛期だった頃の半導体製造を復活させようとしているが、業界専門家は、半導体チップの組み立て/テストメーカー各社による基本的な国内エコシステムを再構築しない限り、その取り組みが成功する見込みはないとみている。 3次元集積化技術「SoIC」の開発ロードマップ

3次元集積化技術「SoIC」の開発ロードマップ

今回は、シリコンダイを3次元積層する技術「SoIC(System on Integrated Chips)」の開発ロードマップを紹介する。 Intelが3つの次世代パッケージング技術を明らかに

Intelが3つの次世代パッケージング技術を明らかに

Intelは、米国カリフォルニア州サンフランシスコで2019年7月9〜11日の日程で開催されている「SEMICON West 2019」に合わせて行われたイベントにおいて、3種類のパッケージング技術に関する同社のロードマップを初めて明らかにした。