TSMC、フィン構造を選べる3nmノードを発表:2nmについても言及

TSMCは、3nm FinFETノードを発表した。2022年後半に量産を開始する予定としている。同技術は、半導体設計における性能と電力効率、トランジスタ密度を向上させることができるだけでなく、これらのオプションのバランスを選択することも可能だという。

TSMCは、3nm FinFETノードを発表した。2022年後半に量産を開始する予定としている。同技術は、半導体設計における性能と電力効率、トランジスタ密度を向上させることができるだけでなく、これらのオプションのバランスを選択することも可能だという。

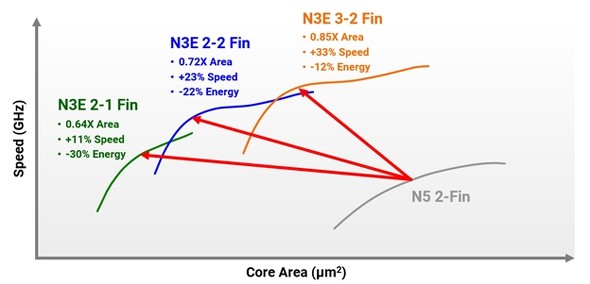

TSMCの3nm技術は、同社の「FinFlex」アーキテクチャを搭載し、性能に優れた3-2フィン構成のスタンダードセルと、電力効率およびトランジスタ密度に優れた2-1フィン構成、効率性能に優れた2-2フィン構成の選択肢を提供する。

FinFlexは、米国カリフォルニア州サンタクララで2022年6月16日(現地時間)に開催された「2022 North America Technology Symposium」で発表された。この新しいアーキテクチャによって、顧客は、さまざまなフィン構成を実装する機能ブロックを使用してSoC(System on Chip)を設計し、性能や電力、ダイサイズの目標を達成できるようになるという。

TSMCのCEO(最高経営責任者)を務めるC.C. Wei氏は、「演算能力とエネルギー効率に対する需要はかつてないほど急速に高まっており、半導体業界に前例のない機会と課題を生み出している」と述べている。

TSMCは、3nmノードの立ち上げ時にさまざまな選択肢を提供することで、プロセス技術のリーダーシップを目指すSamsung ElectronicsやIntelなどライバル企業を引き離すことを狙う。米国の市場調査会社であるGartnerによると、TSMCは先進の7nmと5nmノードで90%のシェアを獲得しているという。

TSMCによると、同社の3nmプロセス技術は、フィン構成を組み合わせられるように設計されている。

TSMCのグローバルマーケティングの責任者を務めるGodfrey Cheng氏は、「EDAパートナーと緊密に連携することで、顧客が、同じツールセットを使用しながら、TSMCのFinFlexを製品に最大限に活用できるようにする」と説明した。

Cheng氏によると、半導体設計における最近のトレンドの1つは、ハイブリッドCPUだという。新しいCPUは、高性能コアと電力効率に優れたコア、GPUコア、固定機能ブロックを備える。電力効率に優れたCPUコアは、日常的なワークロードのほとんどを処理できる。ワークロードが増加すると、高性能コアが動作する。これらのCPUコアを補完するのが、超高効率で超高密度のGPUと固定機能ブロックである。

Cheng氏によると、製品設計者はTSMCのFinFlexを使用することで、他のブロックに影響を与えることなく、全て同じダイ上でこれらの機能ブロックごとにフィン構成を最適化できるという。

TSMCは2022 North America Technology Symposiumで、エッジAI(人工知能)やIoT(モノのインターネット)デバイス向けに演算能力とエネルギー効率を向上させるように設計されたプロセス技術「N6e」を開発中であることも発表した。N6eは、TSMCの7nmプロセスをベースにしている。

2nmプロセスである「N2」についても言及した。N2テクノロジーは、3nmの「N3」よりもさらに進化し、同じ電力で10〜15%の速度向上あるいは、同じ速度で25〜30%の電力削減を実現するという。N2ではナノシートトランジスタアーキテクチャを採用する。2025年に生産を開始する予定だ。

今回のシンポジウムでは、複数のダイを積層して接続する技術「SoIC(System on Integrated Chips)」も紹介した。具体的には、CoW(Chip On Wafer)技術を採用したSoICベースのCPUに、レベル3キャッシュとしてSRAMを積層する技術を説明した。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TSMCが語る「N3」ノードの詳細

TSMCが語る「N3」ノードの詳細

TSMCは現在、「N5」プロセスノード適用製品の生産を順調に拡大しているところだが、それをさらに進化させた「N4」ノードの量産を2021年中に開始する予定だと発表した。また、N4よりもさらなる技術的飛躍を実現するとみられる「N3」ノードについても、2022年後半には量産を開始する計画だという。 2022年の設備投資は400億ドル超に、TSMC

2022年の設備投資は400億ドル超に、TSMC

TSMCは、チップの需要が鈍化するかもしれないという懸念にもかかわらず、生産能力拡大のため2022年に400億米ドル以上を投入する計画をあらためて公表した。 TSMCが2nmにナノシート採用、量産開始は2025年を予定

TSMCが2nmにナノシート採用、量産開始は2025年を予定

TSMCは、2025年に量産を開始する次の2nmノードの生産にナノシート技術を採用した。それにより、HPC(High Performance Computing)システムにおけるエネルギー消費の削減を狙う。 シリコンダイを積層する3次元集積化技術「SoIC」

シリコンダイを積層する3次元集積化技術「SoIC」

今回から、シリコンダイを3次元積層する技術「SoIC(System on Integrated Chips)」を解説する。 デンソーがTSMC熊本工場に400億円出資

デンソーがTSMC熊本工場に400億円出資

TSMC、ソニーセミコンダクタソリューションズ、デンソーは2022年2月15日、TSMCの半導体受託製造子会社Japan Advanced Semiconductor Manufacturing(以下、JASM)に対して、デンソーが約3.5億米ドル(約400億円)の少数持分出資を行うと発表した。この出資により、デンソーはJASMの10%超の株式を取得することになる。