TSMCが2nmにナノシート採用、量産開始は2025年を予定:3nmは「息の長いノード」に

TSMCは、2025年に量産を開始する次の2nmノードの生産にナノシート技術を採用した。それにより、HPC(High Performance Computing)システムにおけるエネルギー消費の削減を狙う。

TSMCは、2025年に量産を開始する次の2nmノードの生産にナノシート技術を採用した。それにより、HPC(High Performance Computing)システムにおけるエネルギー消費の削減を狙う。

競合先であるSamsung ElectronicsとIntelは、早ければ2022年に独自のナノシートデバイスを本格展開する計画であることから、TSMCは2社に後れを取る形になる見込みだ。

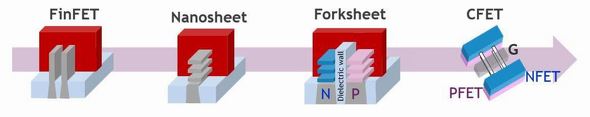

世界をリードするチップファウンドリーであるTSMCは、年次の技術シンポジウムの予告として、少数のニュースメディアに対し今後数年間のロードマップの概要を伝えた。同シンポジウムはこれから数カ月かけて、複数の国/地域で開催される予定だ。TSMCの事業開発担当バイスプレジデントであるKevin Zhang氏によると、同社は、CFET(コンプリメンタリFET)など、ナノシートの後に続くプロセス技術も検証しているという。

CFETはナノシート技術の進化形である。n型FETとp型FETを上下に積層し、より高いトランジスタ密度を実現する。データセンターなどのHPCアプリケーションにおけるエネルギー消費は、地球温暖化に大きく影響している。TSMCは、そのようなエネルギー消費の削減を促す新たなトラジスタ構造を模索している。

Zhang氏は米国EE Timesに対し、「これはトランジスタの一つの選択肢にすぎない。このトランジスタ技術の生産開始については言及できない」と述べた。

二硫化タングステンなど新材料の活用も

TSMCの技術ロードマップのさらに先には、二硫化タングステン(WS2)など研究中の新素材がある。Zhang氏は、二硫化タングステンは、より優れた伝導性とエネルギー効率の高い演算を実現すると述べた。また、電子移動度が高いカーボンナノチューブも検証中だという。

Zhang氏は「こうした新しいデバイスや素材は、当社がスケーリング(微細化)を前進させる上で役立つだろう」と述べた。同氏は、「ムーアの法則」の重要性が損なわれつつある中で、エネルギー効率と低消費電力は、明らかに未来に向けた新たなベンチマークになっていると付け加えた。

TSMCは2022年後半にも、業界をリードする3nmノードの生産を開始する予定だ。市場調査会社のGartnerによると、それにより、5nmノードでTSMCがシェア9割を占めるFinFETの時代は終わりを迎えるという。3nmと2nmの間には約3年の期間があることになる。

「われわれは、3nmが息の長いノードになると確信している。3nmには大きな需要あるとみている。一方、3nmから2nmへの移行に関して言うと、ナノシートは、そのトランジスタ構造によりエネルギーならびに演算効率をさらに高めるという観点から、独自の利点を持つ。演算性能の要件で、エネルギー効率がより求められる製品を必要とする顧客は、まず2nmに移行すると考えている」(Zhang氏)

Samsungは、2022年後半に3nmノードでナノシート技術を初めて導入する予定だ。BernsteinのアナリストであるMark Li氏によれば、それはやや時期尚早かもしれないという。

Li氏はEE Timesに対し、「Samsungは現在、ナノシートを採用しようとしているが、それによりQualcommやNVIDIAなどの顧客が、リスクを懸念してTSMCへと流れる可能性もある」と述べる。「Intelのナノシート採用計画も、TSMCより恐らく1年ほど早いが、Intelが実行できるかどうかは、また別の問題だ。新しいノードを量産化に適用するには、技術的な準備と実効能力を慎重に判断する必要がある。TSMCは、その能力が優れているのだ」(同氏)

TSMCの顧客の中には、より多くの技術的利益を得るために、長く3nmを活用する企業もいるだろう。3nmと2nmはかなりの期間、共存していくのではないか」(Li氏)

ファウンドリーの顧客をFinFETからナノシートのような新しい技術に移行させることは、リスクが高い。だがWedbush SecuritiesのシニアバイスプレジデントであるMatthew Bryson氏によれば、TSMCには顧客を安心させられる実績があるとみている。

「近年の実績を見れば、TSMCが有利なのは確かだ。とはいえ、Intelの投資意欲が以前よりも強く、新しい技術でリードすることを狙っていることから、競争環境は変化している」(Bryson氏)

【翻訳:青山麻由子、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

次々世代のトランジスタ「モノリシックCFET」の製造プロセス

次々世代のトランジスタ「モノリシックCFET」の製造プロセス

今回から、2種類のCFETの製造プロセスを解説していく。始めは「モノリシックCFET」を取り上げる。 次々世代のトランジスタ「シーケンシャルCFET」でシリコンの限界を突破(前編)

次々世代のトランジスタ「シーケンシャルCFET」でシリコンの限界を突破(前編)

今回と次回は「シーケンシャル(Sequential)CFET」の重要な特徴である、ボトム側とトップ側で異なるトランジスタ材料が選べることの利点と、実際にCFETを試作した事例を解説する。 次々世代のトランジスタ「シーケンシャルCFET」の製造プロセス

次々世代のトランジスタ「シーケンシャルCFET」の製造プロセス

今回は、下側(底側、ボトム側)のトランジスタを作り込んでから、その上に別のウエハーを貼り合わせて上側(頂側、トップ側)のトランジスタを作成する「シーケンシャル(Sequential)CFET」の製造プロセスを解説する。 「半導体不足は2024年まで続く可能性」、Intel CEO

「半導体不足は2024年まで続く可能性」、Intel CEO

IntelのCEO(最高経営責任者)であるPat Gelsinger氏は、自動車から高性能兵器までさまざまな製品の生産を制限している、2年に及ぶ半導体不足が、2024年いっぱいまで続くことを確信している。 ソニーのイメージセンサー事業、課題はロジックの調達

ソニーのイメージセンサー事業、課題はロジックの調達

ソニーグループは2022年5月26〜27日にかけて、2022年度の事業説明会を開催した。イメージング&センシング・ソリューション(I&SS)分野については、ソニーセミコンダクタソリューションズの代表取締役社長兼CEO(最高経営責任者)である清水照士氏が報告した。