高度なチップレット技術を提供する米新興企業:Eliyan Corporation

近年、チップレットへの関心が高まっている。米スタートアップのEliyan Corporationは、チップレット向けソリューションを提供する企業の一つだ。

チップレットは近年多くの関心を集めている。そのため、ベストプラクティスの標準化に向けて、最近、「Universal Chiplet Interconnect Express(UCIe)」コンソーシアムが結成された。シリコンバレーのスタートアップ企業であるEliyan Corporation(以下、Eliyan)は現在、ステルスモード(開発状況の詳細を明かさないこと)を脱し、より効率的なパッケージング手法でチップレットエコシステムに貢献できると表明している。

EliyanのCEO(最高経営責任者)を務めるRamin Farjadrad氏は米国EE Timesのインタビューで、「標準的な有機基板上で同種および異種アーキテクチャを接続する費用対効果の高い方法は非常に必要とされており、Eliyanの高性能チップレットインターコネクトはこのニーズに対応できると考えている」と語った。

同氏は、「当社のBoW(Bunch-of-Wires)チップレットシステムは、高度なパッケージング技術を使用したダイツーダイ(D2D)の実装と同様の帯域幅と電力効率、レイテンシを、標準的なパッケージで実現できる。これは、高度なパッケージングのあらゆる欠点や制限を取り除いて、大きな可能性への扉を開く技術である」と述べている。

「ムーアの法則」の終えんは、豊富な並列処理とマルチチップ集積によって実現されるチップレットベースのSiP(System in Package)によって相殺される可能性がある。チップレットベースのSiPは、実装面積が小さく、安価で消費電力が少ないながらも、高い性能を提供できる。

高効率のハードウェア技術の実現を目指す共同コミュニティーである「Open Compute Project(OCP)」は、Eliyanの「NuLink」PHY(物理層)と特許取得済みの「NuGear 2.5/3D」トポロジーソリューションを含むBoWスキームを採用している。NuLink技術は、UCIeと下位互換性がある。Intelが初期仕様を提供したUCIeは、業界標準規格である「PCI Express(PCIe)」および「Compute Express Link(CXL)」を活用し、D2DのI/O PHYやD2Dプロトコル、ソフトウェアスタックモデルの仕様を定めた規格である。

Eliyanは特に、さまざまな機能を1つのパッケージに接続する高効率なD2D PHYのニーズに対応するためにBoWアプローチを開発したという。高効率なD2D PHYは、データセンターやクラウドコンピューティング、AI(人工知能)、グラフィックスなどの幅広い計算集約型アプリケーションに必要な性能と統合を実現するために不可欠である。

同社のNuLink PHY技術は、BoWとUCIeのスーパーセットで、特許取得済みの実装技術を使用してあらゆるパッケージング基板上のD2D接続の電力性能を大幅に差別化するという。加えて、複雑さも軽減して、全体的な開発期間とコストを削減する。

Farjadrad氏は、「当社のソリューションは、あらゆるチップシステムに適用でき、基本的に高度なパッケージングを必要としない」と述べている。

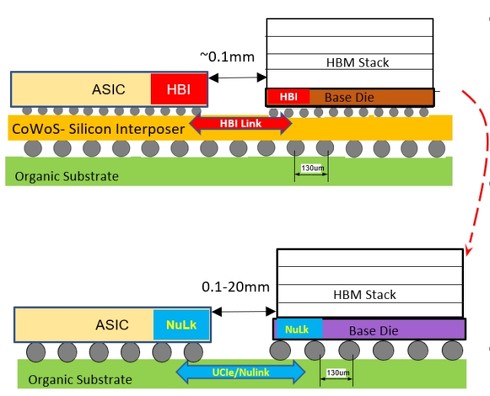

NuLinkの導入によって不要となるこれらの高度なパッケージングソリューションには、シリコンインターポーザーや組み込みマルチダイインターコネクトブリッジ(例えばIntelの「EMIB」)などがある。Farjadrad氏は、「例えば、シリコンインターポーザーはシリコンを1個追加する必要があるため、チップを集積できるエリアが制限されてしまう」と説明している。

これは、性能の制限や、低いウエハーテストカバレッジ(歩留まりに影響する)、TCO(Total Cost of Ownership)の増加、製造サイクル時間の延長につながる可能性があると同氏は述べる。

Eliyanの「Nulink PHY」は、シリコンインターポーザーを排除し、有機基板上で「HBM(High Bandwidth Memory)3」をASICに接続する[クリックで拡大] 出所:Eliyan Corporation

また、NuGearでは、DRAMを含むさまざまなプロセスにおいて、異なるD2Dインタフェースのチップを混在させることが可能になる。Eliyanは、初期のバージョンを14nmプロセスで量産し、商用化に耐えうることと、性能上の利点を証明した。最新バージョンは5nmプロセスでテープアウトし、標準的なパッケージにおいて2000Gbps(ビット/秒)/mmのエッジ帯域幅を実現したとしている。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術

ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術

今回は、「IEDM2020」から先端パッケージの講演をいくつか紹介する。そこで見えてきたのは、今後「ムーアの法則」のけん引役となるかもしれない「チップレット」技術と、その開発競争が進んでいるということだった。 「ムーアの法則」減速への打開策? ヘテロジニアス設計

「ムーアの法則」減速への打開策? ヘテロジニアス設計

半導体業界では現在、IoT(モノのインターネット)やビッグデータ、AI(人工知能)などによる新しい成長の波が押し寄せている。しかし、半導体イノベーションの必要性がこれまで以上に高まっているにもかかわらず、従来型のムーアの法則の2D(2次元)微細化は、減速の一途にある。 データセンター用RISC-Vチップレットの製品化を加速

データセンター用RISC-Vチップレットの製品化を加速

米国のVentana Micro Systems(以下、Ventana)は、2021年にステルスモードを脱して以降、パートナーや潜在顧客との関係構築を精力的に進め、RISC-Vベースのチップレットのけん引力を生み出してきた。米国EE Timesは、2022年7月10〜14日に米国カリフォルニア州サンフランシスコで開催された「59th Design Automation Conference(DAC 2022)」でBaktha氏に独占インタビューを行った。 Intel、TSMCを活用しつつ「リーダーシップを取り戻す」

Intel、TSMCを活用しつつ「リーダーシップを取り戻す」

Intelが、かつてのライバルであったTSMCへの依存度を高めている。売上高を増加させ、最終的に製造規模と半導体プロセス技術分野において世界リーダーとしての優位性を取り戻していきたい考えのようだ。 チップレットが主流になるための2つの要素

チップレットが主流になるための2つの要素

現在、データセンターのワークロードが急激な進化を遂げている。計算やメモリ、IOなどの機能が変化しながら組み合わさって、より高い計算密度が求められるようになってきた。このためアーキテクチャは、従来の「One-size-fits-all」型のモノリシックなソリューションから、ディスアグリゲーション(分離)された機能へと移行が進み、特定用途向けとして個別にスケーリングすることが可能になっている。 10年で5世代の進化を遂げた高性能パッケージング技術「CoWoS」(前編)

10年で5世代の進化を遂げた高性能パッケージング技術「CoWoS」(前編)

今回からは、高性能コンピューティング(HPC)向けパッケージング技術「CoWoS(Chip on Wafer on Substrate、コワース)」を解説する。