光インターコネクトの新しい指標:光伝送技術を知る(23) 光伝送技術の新しい潮流と動向(4)(3/3 ページ)

今回は、これからの光インターコネクトに求められる指標について解説する。

Energy Efficient (pJ/Gbit)

インターコネクトのFOMの分母はpJ/bit、エナジー効率(Energy Efficiency)である。mW/Gbitと等価であり、いつの時代にも低減が要求されるパラメータである。まず5pJ/bitを目指し、将来は<1pJ/bitを達成すべきだという意見が多いようだ。これは、「100Gbit/s per laneをEnd-to-End計算で500mWを達成」という目標にも置き換えられる。現在の8x100Gbit光トランシーバー(QSFP-DDやQSFP)が、10〜15pJ/bit(消費電力で8〜12W)と予測されているので、かなり厳しいターゲットだ。

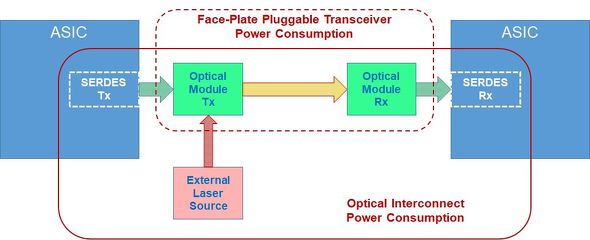

ところで、最近はEnergy Efficiencyの定義が話題となっている。光インターコネクトという考え方からするとASICの入出力回路(SERDES)間の全消費電力が対象だという意見が増えているようだ。図4に光インターコネクトの主要なブロックを示した。ASICのSERDES Tx、Optical Module Tx、Optical Module Rx、ASIC SERDES Rxで構成される。つまり、ASICの入出力回路と光インターコネクトモジュールの消費電力の合計である。もし、External Laser Source (ELS)使用の場合はその消費電力を加算しなければいけない。

Front-Panel Pluggableのエネルギー効率では光モジュール(Optical Module)だけが対象だったが、それだけで既に10〜15pJ/bitであり、目標の5pJ/bitがいかに厳しいかが分かるだろう。さまざまな工夫が必要になるので、新しい方式や回路など挑戦的な展開が予想される。

ことし(2023年)のOFCにおける話題の一つは、Linear Drive Pluggable Optics(LPO)であった。Aristaが先導してPlenaryやパネルなどで紹介し、MACOMがSMFとMMFトランシーバーの動態展示を行った。その肝は、「TransceiverにDSPを搭載せずにSERDES間で伝送を可能にして、Transceiverの消費電力を半分に低減すること」である(コストの大幅な低減も期待できる)。電力を半減した800G (8×100G) LPO (QSFP-DD)を用いれば、51.2TスイッチBoxの消費電力をシャシーの最大許容電力である約1.5kW以下にできるという。相互互換性など簡単ではない課題も多いが、そのモーメンタムを止めることは難しく、ハイパースケールデータセンターではFront Panel (FP) Pluggableが引き続き主流であることを確実にしたと考えている。

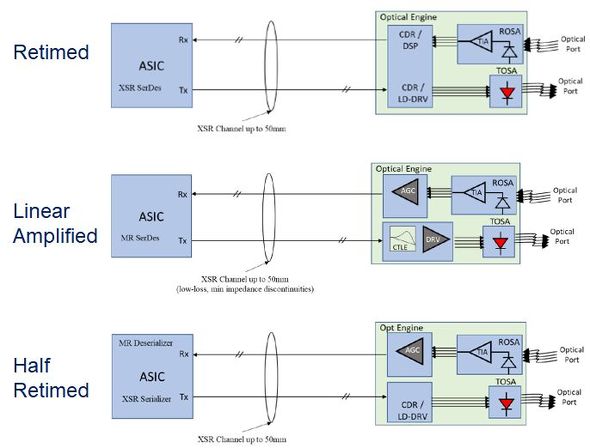

このLPOはFP Pluggableにとどまらず、光インターコネクト開発に勇気を与えた。図5はOIF Co-package Optics (CPO) Framework Document[5]に示されたCPOの方式である。FP Pluggableの主流が、送受信にClock and Data Recovery (CDR)を有し、電気と光伝送規格を分離するRetimed方式である。例えばOIF-CEIで電気、Ethernetで光の規格作りが同期して進められている。DSPは方式の本質ではないが、特にPAM4変調信号伝送では有効であり、CDRと集積化されほとんどの光モジュールに搭載されている。しかし、消費電力やLatencyが大きいという問題がある。これに対し、DSPを用いないRetimed方式として”OpenEye” MSAの提案が提案され、消費電力を20%低減できるという。

[5] “Co-Packaging Framework Document,” OIF-Co-Packaging-FD-01.0, February 3, 2022

一方、Optical ModuleにCDR(そしてDSP)を搭載しない方式がLinear Amplified方式である。送信電気信号の回路基板などによる伝送劣化をCTLE回路などで補償し光出力波形を整える。光受信信号は光受信部でLinearに増幅され、等化回路(Equalizer)とCDRはASICのSERDES Rxに搭載する。もともとSERDESには電気信号伝送の等化回路が搭載されていて、それを拡張するのだ。BroadcomのEthernetスイッチIC「StrataXGS Tomahawk 5」のSERDESのEqualizerがLinear Amplifiedに対応可能なDigital(DSP)であったことから、LPOが実現したといわれている。

この方式の鍵は3つある。一つは光送信部のCTLEを用いたPre-Emphasisを調整して良質な光波形を出力することである。Aristaの発表では広帯域なDriver回路と表現されており、必要十分なアイ開口が得られていると考える。DSPを前提とした光出力信号品質パラメータであるTDECQで1dB程度以下(Ethernet規格は<3.5dB)というMACOMの報告もあるようだ。アイ開口を改善してDSPを排除する方式を提案している“OpenEye” MSA[6] (MACOMもメンバー)規格に適合しているかは不明である。

[6] https://www.openeye-msa.org/

2つ目は、伝送損失や波形劣化である。もし、光送信波形が良好だとすると、2km程度の短距離ではその波形はほとんど劣化せずに届くので、劣化は光受信部とモジュールからSERDES間のPCB上帯域劣化(伝送損失)に起因する。Aristaの発表では広帯域なTIA(Trans-Impedance Amplifier、受信アンプ)回路と表現があり、光受信部の帯域は広いのだろう。PCBの帯域劣化に関しては、低Dk/Df(比誘電率/誘電損失係数)の高周波基板を使用したという話である。基板は高価だが低コストのLPOではトータルコストで吸収できるという。それにより光トランシーバー(QSFP-DD)ソケットを介してPCB配線を含めて11dB@28GHzの低損失を実現したという。

最後は、SERDES Rxである。今回の実験で使用したBroadcomのStrataXGS Tomahawk 5ではSERDES RxにDSPが使用されているという。11dBの損失であればOIF-112G-XSRの10dBにも近く、現在CPO(NPO)向けに標準化中の-XSR+の仕様内であろう。Aristaの発表ではCPOと消費電力などで有意差はないとまで言い切っていた。

光インターコネクトはMassive Node ComputeのPoolingされた多数のGPU間やGPU-メモリ間接続のためICパッケージの近くあるいは中に搭載され低損失電気配線が可能である。CPOで議論されているLinear Amplified方式の光インターコネクトをASICと同一基板に実装すれば-XSRあるいは-XSR+の損失を実現できると見込まれている。

さらに、このLPOでは、FECを用いることなく1e-8以下の低BERをSi-photonicsを使用して実現しており、FEC無しあるいはLite FECが適用可能であり、これにより低Latency接続を実現できる。

弱点として、送信波形は光送信部の入力波形に影響されるため、相互互換性や性能保証(試験)などの課題が残っている。そこで、送信部入力信号をOptical Moduleでいったん終端する、Half Retimed方式(図5)が提案されている。これにより光出力波形が光送信部入力波形に依存しなくなり、試験も容易である。PCIeあるいはUCIeでは送信Clock供給(Forward Clock)により、回路の簡素化や低消費電力化を実現することができるため、Half Retimed方式が有用だとみている。先駆けとなった“OpenEye” MSAが参考になると考えている。

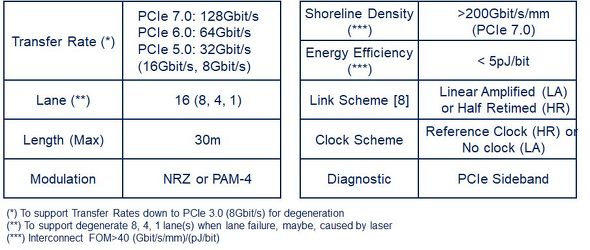

以上から前回示した光インターコネクト仕様にShoreline DensityとEnergy Efficiencyを追加したのが表1である。いくつかの重要な数字がAyar Labsなどが示したもの[7]と同じなのは偶然ではなく、光インターコネクトを検討すると同じところに行きつくということだと考えている。

[7] “Disaggregation and Optical Interconnect in AIHPC Networks,” Lightwave Webcast, Jun. 9th, 2023

光インターコネクトの実現に関連した事例を次回以降に考察したい。

筆者プロフィール

高井 厚志(たかい あつし)

30年以上にわたり、さまざまな光伝送デバイス・モジュールの研究開発などに携わる。光通信分野において、研究、設計、開発、製造、マーケティング、事業戦略に従事した他、事業部長やCTO(最高技術責任者)にも就任。多くの経験とスキルを積み重ねてきた。

日立製作所から米Opnext(オプネクスト)に異動。さらに、Opnextと米Oclaro(オクラロ)の買収合併により、Oclaroに移る。Opnext/Oclaro時代はシリコンバレーに駐在し、エキサイティングな毎日を楽しんだ。

さらに、その時々の日米欧中の先端企業と協働および共創で、新製品の開発や新市場の開拓を行ってきた。関連分野のさまざまな学会や標準化にも幅広く貢献。現在はコンサルタントとして活動中である。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

CXLはデータセンターの「救世主」となるのか

CXLはデータセンターの「救世主」となるのか

AI(人工知能)の普及でデータ量が爆発的に増大し、データセンターにかかる負担が増加する中、その課題解決の鍵はCXL(Compute Express Link)インタフェースが握っている。 チップレットの普及拡大へ、「UCIe 1.0」が登場

チップレットの普及拡大へ、「UCIe 1.0」が登場

UCIe(Universal Chiplet Interconnect Express)は、パッケージ内のチップレットの相互接続を定義するオープン規格だ。UCIe策定の参加メンバー企業は、Advanced Semiconductor Engineering(ASE)、AMD、Arm、Google Cloud、Intel、Meta、Microsoft、Qualcomm、Samsung Electronics、TSMCの10社である。【訂正あり】 高度なチップレット技術を提供する米新興企業

高度なチップレット技術を提供する米新興企業

近年、チップレットへの関心が高まっている。米スタートアップのEliyan Corporationは、チップレット向けソリューションを提供する企業の一つだ。 Massive Computeデータセンターへの期待

Massive Computeデータセンターへの期待

光技術や光モジュール開発の動向をお伝えするシリーズ。今回は、データセンターの新しい動向を解説したい。 「光トランシーバー」は光伝送技術の凝縮

「光トランシーバー」は光伝送技術の凝縮

今回から、光トランシーバーについて解説する。データセンター、コンピュータや工場内ネットワークで使用される80km程度以下の中短距離光リンクを中心に、ストレージ、ワイヤレスやアクセス通信ネットワークなど、多様なアプリケーションで使用されている光トランシーバーを紹介する。 光ファイバーとシリコン光導波路を結合する技術

光ファイバーとシリコン光導波路を結合する技術

今回は、光ファイバーとシリコン光導波路を結合する技術を解説する。