わずか3個のLSIでモバイル超音波診断装置を実現、ソシオネクスト:Medtec Japan 2024

ソシオネクストは「Medtec Japan 2024」(2024年4月17〜19日)に出展し、同社が開発したワイヤレス超音波診断装置専用のLSIを展示した。同LSIの活用により、従来のワイヤレス超音波診断装置に比べて、必要なチップ数を半分に削減できるという。

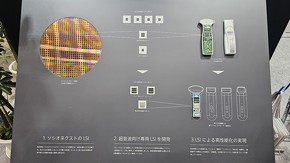

ソシオネクストは「Medtec Japan 2024」(2024年4月17〜19日/東京ビッグサイト)に出展し、同社が開発したワイヤレス超音波診断装置専用のLSI「viewphii(ビューフィー) 64」や、同LSIを搭載したワイヤレス超音波プローブ(プロトタイプ)を展示した。

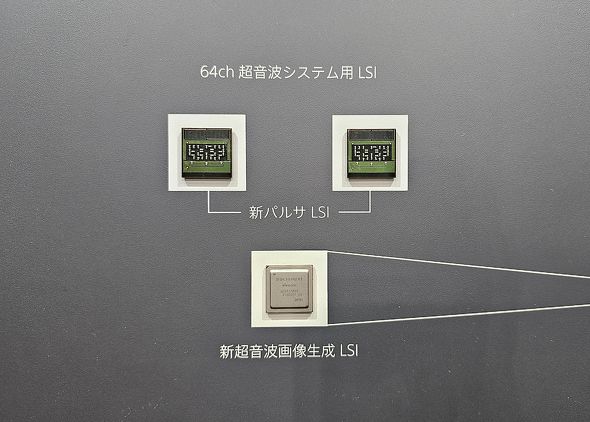

viewphii 64には、「パルサLSI」「超音波画像生成LSI」の2種がある。パルサLSIは、超音波振動子の64素子を同時に駆動する機能と、受信した微弱信号を後段のLSIに送るためのアナログスイッチ機能を備えている。超音波画像生成LSIは、パルサLSIから受け取った微弱信号を増幅し、A-D変換や整相加算をするビームフォーマー機能および超音波画像を生成する機能に加え、システム全体の制御を行うための機能を搭載している。

同社 メディカルソリューションチーム ビジネス開発部 ビジネス開発課 課長の小林真理氏は、viewphii 64の特長について「超音波用途では、ノイズの影響が強く出やすいため、ノイズの影響を最小限に抑えられるように設計を工夫している。既に医療用途での使用に必要な認証を取得していて、性能も市場に出せるレベルだ」と説明した。

ワイヤレス超音波プローブ(プロトタイプ)もソシオネクストが自社開発したものだ。前世代品「viewphii-US」では3種類/計6個のLSIを搭載していたのに対し、最新のプロトタイプでは、パルサLSIが2個と超音波画像生成LSIが1個、つまり2種類/計3個のチップでワイヤレス超音波プローブを構築できる。

viewphii 64を使用したプローブは、Tx(送信)側は最大192チャネル、Rx(受信)側は64チャネルを備える。前世代品よりも小型化しながら、消費電力は同等性能の1W(代表値/Bモード時)に抑えている。また、画像処理機能として、空間コンパウンド、トラペゾイドスキャンなどの拡張にも対応したことで、より高精細な画像描写が可能になった。

なお、展示したワイヤレス超音波プローブはサンプル品で、今後もプローブそのものの販売は行わないという。

今後の課題について小林氏は「ワイヤレス超音波診断装置の発展により、一般人(非医療従事者)によるセルフ検査は普及していくだろう。一方で、検査結果の読影に関しては専門的な知識が必要だ。今後は、ソフトウェアやAI(人工知能)などのソリューションとも連携して、一般人でも使いやすいような環境を整えていく必要がある」と語った。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

トヨタやルネサスなど12社、車載用SoC開発に向け新組織「ASRA」を設立

トヨタやルネサスなど12社、車載用SoC開発に向け新組織「ASRA」を設立

トヨタ自動車やデンソー、ルネサス エレクトロニクスなど自動車メーカー、電装部品メーカー、半導体関連企業12社が、「自動車用先端SoC技術研究組合(Advanced SoC Research for Automotive/ASRA)」を2023年12月1日付で設立した。チップレット技術を適用した車載用SoC(System on Chip)の研究開発を行う組織で、2030年以降の量産車に搭載すべく、研究開発を進める。 車載用3nmプロセス採用SoCを26年に量産、ソシオネクスト

車載用3nmプロセス採用SoCを26年に量産、ソシオネクスト

ソシオネクストが、TSMCの車載向け3nmプロセス「N3A」を採用したADASおよび自動運転向けカスタムSoC開発に着手した。2026年の量産開始を予定している。 ソシオネクスト、2nm技術でArmおよびTSMCと協業

ソシオネクスト、2nm技術でArmおよびTSMCと協業

ソシオネクストは、2nm世代プロセスのマルチコアCPUチップレット開発で、ArmおよびTSMCと協業する。開発するチップレットは、大規模データセンター用サーバや5G/6Gインフラストラクチャ、DPU(データプロセシングユニット)、ネットワークエッジ市場に向け、2025年上期にもES品の供給を始める。 ソシオネクスト、HD-PLC通信用LSIの量産を開始

ソシオネクスト、HD-PLC通信用LSIの量産を開始

ソシオネクストは、量産出荷を始めたHD-PLC通信用LSI「SC1320A」が、札幌市に開業する都市型水族館「AOAO SAPPORO」の高速電力線通信システムに採用されたと発表した。 一般的な中性子源で、半導体ソフトエラー率を評価

一般的な中性子源で、半導体ソフトエラー率を評価

量子アプリ共創コンソーシアム(QiSS)で、京都大学大学院情報学研究科の橋本昌宜教授が主導する産学連携のソフトエラー研究グループは、一般の中性子源を用いて、半導体チップの地上ソフトエラー率を評価する方法を開発した。