膜形成時の泡を98%削減 ウエハーの歩留まり向上に効く:先進パッケージング用に開発(2/2 ページ)

東京エレクトロンと太陽ホールディングス(太陽HD)は2024年6月5日、半導体実装/材料分野の最新技術に関するプレス向けセミナーを実施した。東京エレクトロンは次世代の塗布現像機に実装予定の膜形成手法や塗布手法を、太陽HDは、半導体の3次元積層に向けて研究開発を進めている高解像度感光性絶縁材料を紹介した。

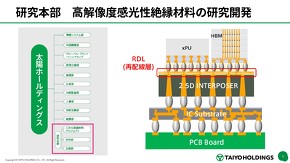

3次元積層向けの高解像度感光性絶縁材料

太陽HDは、半導体の3次元積層に向けて研究開発を進めている高解像度感光性絶縁材料を紹介した。

太陽HD 研究本部三次元実装材料プロジェクトリーダーの緒方寿幸氏によると「現在、半導体の3次元積層に向け再配線層(RDL)の微細化の研究が加速している。RDLの微細化を達成するために、高解像度感光性絶縁材料の開発が求められている」という。

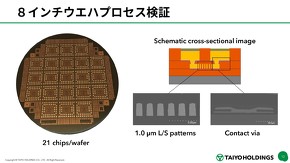

同社は、2022年に再配線層に関する研究本部を立ち上げ、高解像度感光性絶縁材料の研究開発を開始した。開発中の感光性絶縁材料の感光性はネガ型で、露光波長はi-line(λ=365nm)、L/S(ラインアンドスペース)は0.7μm/0.7μmだ。

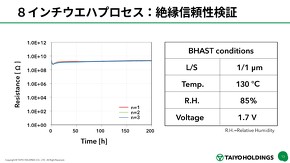

既に、8インチウエハーでは、電気特性テストなどのプロセス検証を達成している。同技術は、CLEAN TRACK LITHIUS Pro APなどでも使用できる。

緒方氏は、「今後は、12インチウエハーでのプロセス検証に取り組み、2026年までの提供開始を目指す」と語った。同技術においては、ベルギーの研究機関imecの「3Dプログラム」に参加して、共同開発に着手しているという。

土屋氏は、「後工程分野は、信頼性への要求が高まっている。要求に応えるためには、半導体装置メーカーや材料メーカーがそれぞれに研究開発を進めるだけでなく、連携しながら技術開発を進めることが不可欠だ」と連携の重要性を語った。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「チップレット構想」は破綻してないか? 利点はどこに

「チップレット構想」は破綻してないか? 利点はどこに

昨今、盛り上がっている「チップレット」だが、最近の発表を聞いているとどうにも違和感を覚えてならない。IntelやAMDの製品を取り上げながら、当初提唱されていたチップレットの利点について、もう一度考えてみたい。 エレクトロニクスとパッケージ、部品、実装設備の動向を590ページに積載

エレクトロニクスとパッケージ、部品、実装設備の動向を590ページに積載

電子情報技術産業協会(JEITA)が2年ぶりに実装技術ロードマップを更新し、「2024年度版 実装技術ロードマップ」を2024年6月に発行した。ついに電子書籍となった。2024年6月11日には、5年ぶりとなるリアルでの「完成報告会」を都内で開催した。 半導体後工程の自動化を推進、インテルやオムロンらが「SATAS」を設立

半導体後工程の自動化を推進、インテルやオムロンらが「SATAS」を設立

半導体メーカーや半導体製造装置/自動搬送装置メーカーおよび標準化団体など15の企業・団体は、2024年4月16日付で「半導体後工程自動化・標準化技術研究組合(SATAS)を設立した。2028年の実用化を目指し、半導体後工程の完全自動化や標準化に取り組む。 DUVレーザーで半導体基板に直径3μmの穴あけ加工

DUVレーザーで半導体基板に直径3μmの穴あけ加工

東京大学と味の素ファインテクノ、三菱電機、スペクトロニクスの4法人は、深紫外(DUV)レーザー加工機を用い、半導体基板の層間絶縁膜に直径3μmという微細な穴あけ加工を行う技術を開発した。次世代チップレットの製造工程などに適用していく。 RapidusとIBM、2nm世代半導体のチップレットパッケージ技術で協業へ

RapidusとIBM、2nm世代半導体のチップレットパッケージ技術で協業へ

RapidusとIBMは2024年6月4日、2nm世代半導体のチップレットパッケージ量産技術確立に向けたパートナーシップを締結したことを発表した。RapidusはIBMから高性能半導体向けのパッケージ技術の提供を受け、技術確立の協業を進める。