銅配線を2nmノード以下に微細化、Appliedが新材料:最大25%の低抵抗化も実現(2/2 ページ)

Applied Materialsが、銅配線の2nmノード以降への微細化と最大25%の低抵抗化を実現する新材料技術を開発した。チップの静電容量を低減し、3D積層ロジック/DRAMチップの高強度化も実現する。

Low-k絶縁材料「Black Diamond」を強化

こうした課題に対応するため、より微細なノード向けに低抵抗の銅配線を微細化できるような、新しい材料ソリューションが必要となる。Applied Materialsの半導体製品グループのプレジデントを務めるPrabu Raja氏は、「これらのLow-k誘電体材料は、3Dスタッキングを新たな高みに引き上げるために、静電容量を低減し、チップを強化するはずだ。AI時代には、よりエネルギー効率の高いコンピューティングが必要であり、チップの配線とスタッキングは性能と消費電力にとって非常に重要だ」と述べている。

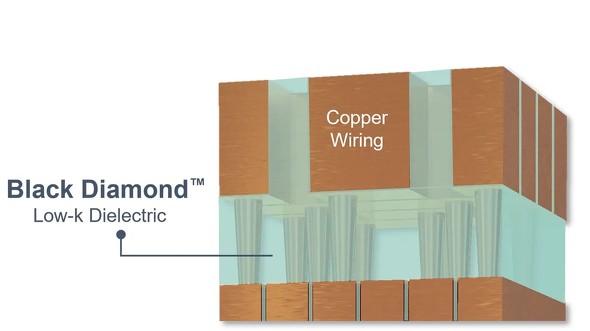

Applied MaterialsのLow-k絶縁材料「Black Diamond」は数十年の実績がある。誘電率定数(k値)が低く、電荷の蓄積を抑えるよう加工されたこの薄膜材料で銅線を覆うことで、電力消費の増大と電気信号間の干渉を抑えることが可能となる。同社が今回発表したのは、2nmノード以下の微細化の実現に向けて、最小k値をさらに引き下げたBlack Diamondの強化版だ。

最新のBlack Diamondは3Dロジックやメモリのスタッキングの機械的強度を高めながら、2nmノード以下へのスケーリング実現をサポートする[クリックで拡大] 出所:Applied Materials

強化版Black Diamondは、機械的強度も向上している。機械的強度は、半導体メーカーやシステム企業が3Dロジックやメモリのスタッキングを進める上で極めて重要となる。Applied Materialsによると、複数のロジックおよびDRAMメーカーがこの最新のBlack Diamond技術を採用しているという。

6つの異なる技術を1つの高真空システムに統合

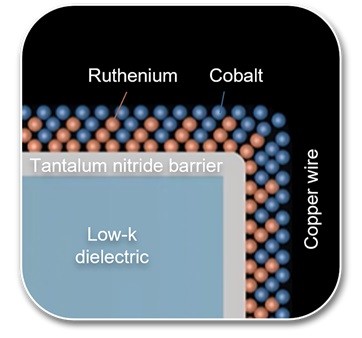

Applied MaterialsはSEMICON West 2024で、6つの異なる技術を1つの高真空システムに統合した「Integrated Materials Solution(IMS)」も発表した。これには、半導体メーカーが銅配線を2nmノード以下に微細化できるようにする材料の組み合わせも含まれる。

これは、ルテニウムとコバルトを組み合わせた二元金属(RuCo)を用いたもので、ライナー厚を33%減らし2nmにするとともに、表面特性を改良してボイドフリーの銅リフローを可能にし、電線抵抗を最大25%引き下げてチップのパフォーマンスと消費電力を改善する。

近年、パターニングの進歩やそれに伴うチップのリソグラフィのスケーリングが話題になっているが、ノードの微細化は、銅配線が物理的なスケーリングの限界に達することにもつながる。ここで概説した材料工学の進歩は、銅配線を2nmノード以下に微細化することで、チップのワット当たりの性能を向上させるように設計されている。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

AIによる技術革新を加速させるTSMCの最新技術

AIによる技術革新を加速させるTSMCの最新技術

TSMCは横浜で開催した顧客向け技術発表会「TSMC Technology Symposium」に合わせ、テクノロジー専門メディア向けの技術説明会を開催した。説明会では、AIイノベーションを加速させるための半導体製造プロセス「TSMC A16」技術や「TSMC System-on-Wafer(TSMC-SoW)」などについて、その概要を紹介した。 Rapidusの顧客は十分にいるのか 米アナリストの見解

Rapidusの顧客は十分にいるのか 米アナリストの見解

RapidusのCEO(最高経営責任者)である小池淳義氏は、米国EE Timesのインタビューに応じ、2025年4月に2nm世代半導体製造のパイロットラインを稼働予定であると語った。Rapidusを訪問したアナリストによると、TSMCとSamsung Electronicsの新たな競合となるRapidusには、この先まだ大きな障壁が立ちはだかっているという。 驚異的な成長で装置メーカートップに躍り出たASML 背景にEUVと中国の「爆買い」

驚異的な成長で装置メーカートップに躍り出たASML 背景にEUVと中国の「爆買い」

現在、EUV(極端紫外線)露光装置の唯一のサプライヤーであるオランダASMLの売上高が「絶好調」だ。本稿では、ASMLの過去3年間の売上高を分析し、ASMLの成長の変曲点を特定する。さらに、今後のASMLの成長を展望する。 線幅サブミクロンも視野に パッケージ向け露光装置でウシオとAppliedが協業

線幅サブミクロンも視野に パッケージ向け露光装置でウシオとAppliedが協業

ウシオ電機とApplied Materialsは2023年12月、戦略的パートナーシップの締結を発表した。両社が「DLT(Digital Lithography Technology)」と呼ぶ、半導体パッケージ基板向けの新しいダイレクト露光装置を早期に市場に投入し、大型化や配線の微細化など半導体パッケージ基板への要求に応えることを目指す。 Applied、40億ドルで米国に半導体R&D施設を新設へ

Applied、40億ドルで米国に半導体R&D施設を新設へ

Applied Materialsは最大40億米ドルを投じ、米国シリコンバレーの同社敷地内にR&D施設を新設すると発表した。施設では半導体メーカー各社が専用スペースを構え、次世代プロセス/装置の早期提供を受けることが可能になるという。 さらなる微細化に向けたEUV/GAA向け技術

さらなる微細化に向けたEUV/GAA向け技術

Applied Materialsの3D GAA(3次元Gate-All-Around)トランジスタ技術とEUV(極端紫外線)リソグラフィソリューションの最新ポートフォリオは、ムーアの法則による2D(2次元)スケーリングの限界に対処するために設計された。EUVによる2Dスケーリングの拡張を熱望する半導体メーカーのために電力効率と性能、面積、コスト、市場投入までの期間(PPACt:Power efficiency, Performance, Area, Cost, and time to market)を改善することを目指している。