「CMOS/スピントロニクス融合AI半導体」を開発:エッジ機器向けに大容量MRAM搭載

東北大学とアイシンは、エッジ機器に適した大容量MRAM搭載の「CMOS/スピントロニクス融合AI半導体」を開発した。システム動作シミュレーションで検証したところ、従来に比べ電力効率は10倍以上、起動時間は10分の1以下となった。

従来に比べ電力効率10倍以上、起動時間10分の1以下に

東北大学とアイシンは2024年10月、エッジ機器に適した大容量MRAM搭載の「CMOS/スピントロニクス融合AI半導体」を開発したと発表した。システム動作シミュレーションで検証したところ、従来に比べ電力効率は10倍以上、起動時間は10分の1以下となった。

新エネルギー・産業技術総合開発機構(NEDO)は、「省エネAI半導体及びシステムに関する技術開発事業」に取り組んでおり、エッジ機器に適した半導体デバイスの早期実現を目指している。この中で、東北大学やアイシン、NECは、CMOS/スピントロニクス融合技術によるAI処理半導体の設計効率化と実証および、その応用技術に関する研究開発を共同で行ってきた。

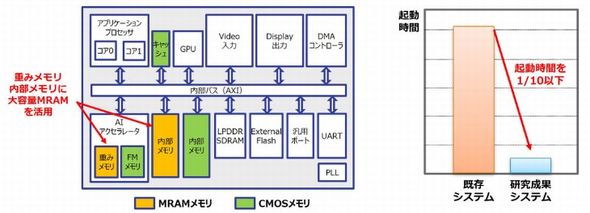

今回は、東北大学がMRAMを用いた自動設計環境の構築とそれに基づくAIアクセラレーターを開発。アイシンは、このAIアクセラレーターとアプリケーションプロセッサや周辺IPを統合した実証用チップのアーキテクチャ設計を担当した。

実証用チップは、内部メモリと重みメモリにMRAMを用い、ニアメモリ・コンピューティング構造とした。この結果、外付けFLASHメモリを採用した従来システムでネックとなっていたバス帯域不足を解消している。

実証用チップには、東北大学国際集積エレクトロニクス研究開発センターが開発した消費電力の小さい「AIアクセラレーター」を搭載。重みメモリや内部メモリにMRAMを用いたことで、従来のSRAMに比べ待機電力や動作電力を大幅に削減できるという。起動時間の短縮と外付けメモリ容量の削減も可能となり、チップの小面積化および低消費電力化を図ることができる。

アイシンは東北大学と協力し、RTLによるシステム動作シミュレーション検証を行った。この結果、従来に比べて電力効率は10倍以上、起動時間は10分の1以下という改善効果を確認した。

実証用チップは、MRAM混載に対応したTSMCの「次世代16nm FinFETプロセス向けPDK」を用いて設計した。アプリケーションプロセッサには「Arm Cortex-A53デュアルコア」を搭載している。

なお、今回の成果は現在幕張メッセで開催中の「CEATEC 2024」にも展示されている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

リチウムイオン電池超える「超高速充放電亜鉛二次電池」、産学連携で開発へ

リチウムイオン電池超える「超高速充放電亜鉛二次電池」、産学連携で開発へ

山形大学は、大阪ソーダやエムテックスマートと連携し、「革新的ナノ均一構造正極による超高速充放電亜鉛二次電池」の開発を行う。資源リスクが低い亜鉛金属を用い、現行のリチウムイオン二次電池を超える電池容量の実現を目指す。 「2年ごとに新世代を投入」ロームがSiC MOSFET開発を加速、25年の第5世代以降

「2年ごとに新世代を投入」ロームがSiC MOSFET開発を加速、25年の第5世代以降

ロームはSiC MOSFETの開発を加速し、2025年に予定する第5世代品のリリース以降、2027年には第6世代、2029年に第7世代と2年ごとに新世代品を投入する計画を明かした。1世代ごとにオン抵抗を30%削減するという。 RapidusとIBM、2nm世代半導体のチップレットパッケージ技術で協業へ

RapidusとIBM、2nm世代半導体のチップレットパッケージ技術で協業へ

RapidusとIBMは2024年6月4日、2nm世代半導体のチップレットパッケージ量産技術確立に向けたパートナーシップを締結したことを発表した。RapidusはIBMから高性能半導体向けのパッケージ技術の提供を受け、技術確立の協業を進める。 リチウムイオン電池の発火を防げるか 開発コンテストで賞金1000万円をつかみ取れ!

リチウムイオン電池の発火を防げるか 開発コンテストで賞金1000万円をつかみ取れ!

新エネルギー・産業技術総合開発機構(NEDO)は2024年4月10日、懸賞金型の研究開発コンテストの第2弾の公募を開始した。テーマとなるのはリチウムイオン電池(LiB)。近年課題になっている、ごみ回収におけるLiBの発火や爆発などを防ぐ技術の開発を促進する。 Rapidusへの政府支援は累計9200億円に、後工程プロジェクトも発進

Rapidusへの政府支援は累計9200億円に、後工程プロジェクトも発進

Rapidusは2024年4月2日、新エネルギー・産業技術総合開発機構(NEDO)に提案し、採択された先端半導体前工程のプロジェクトの2024年計画/予算が承認され、また、新たに提案していた先端半導体後工程のプロジェクトが採択されたと発表した。追加の支援額は、前工程プロジェクトが最大5365億円、後工程プロジェクトが最大535億円だ。 Rapidusとの連携も視野に――「ASRA」が車載用SoCの開発計画を発表

Rapidusとの連携も視野に――「ASRA」が車載用SoCの開発計画を発表

自動車用先端SoC技術研究会(Advanced SoC Research for Automotive/ASRA)は2024年3月29日、記者説明会を開催し、車載用SoC(System on Chip)の開発計画などについて語った。スズキと日立AstemoがASRAに加入したことも併せて発表し、「設立当初から参画を予定していた14社がようやく出そろった」とコメントした。