半導体後工程特集

「ムーアの法則(Moore’s Law)」の終焉が唱えられる昨今、半導体後工程による性能向上に注目が集まっている。本特集では、半導体後工程の最新技術や市場動向を紹介する。

Top Story

台湾企業と提携:

オキサイドは2026年2月、レーザー微細加工装置メーカーである台湾Boliteとの業務提携に基本合意した。今回の合意に基づき両社は、半導体後工程に向けたレーザー微細加工装置事業を本格的に展開していく。

26年からの後工程委託に向け:

ロームがインドの新興半導体メーカーと製造で協業する。ロームはパワーデバイスおよびIC製品について後工程の委託を検討。2026年の量産出荷に向けた技術評価を進めているという。

技術動向

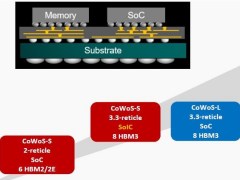

福田昭のデバイス通信(507) TSMCが解説する最新のパッケージング技術(4):

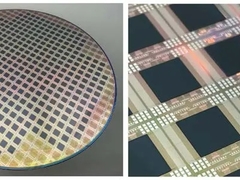

前回に続き、「IEDM 2025」におけるTSMCの講演内容を紹介する。TSMCの2.5次元パッケージング技術「CoWoS(Chip on Wafer on Substrate)」において、インターポーザを低コスト化する技術を解説する。

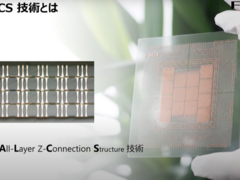

SEMICON Japan 2025:

FICTは「SEMICON Japan 2025」で、次世代半導体パッケージ向けのガラスコア基板「G-ALCS(Glass All-Layer Z-connection Structure、ジーアルシス)」を参考出展した。薄いガラスを何枚も接着して多層化することで、反りやセワレを抑えられる。

複数の基板を貼り付けて切断:

ディスコが、最大400mm角のパッケージを切断できるフルオートダイシングソー「DFD6080」を開発した。2026年下期から販売を始める。

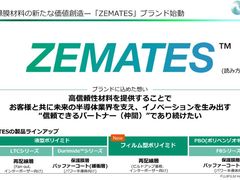

RDL用フィルム型ポリイミドなど:

富士フイルムが、半導体製造の後工程向け感光性絶縁膜材料の新ブランド「ZEMATES(ゼマテス)」を発表した。2030年度までに、感光性絶縁膜材料の売上高を5倍以上に成長させるという。

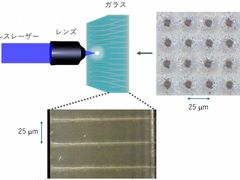

25μm間隔で穴径は10μm以下:

東京大学は、次世代半導体向けガラス基板に対し、極めて微細な穴あけを高いアスペクト比で実現できる「レーザー加工技術」を開発した。ガラス基板はAGC製の「EN-A1」を用いた。

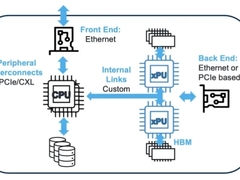

AIデータセンターに対応:

電力効率やコストが懸念されるAIデータセンターでは、チップレット集積の適用が現実的だとされる。チップレット集積技術の進化の鍵を握るのが、インターコネクト技術だ。

2026年から量産開始:

レゾナックは、次世代半導体パッケージ基板向けに熱膨張係数が小さい「銅張積層板」を開発した。温度サイクル試験により従来製品に比べ4倍の寿命を確認、100mm角を超えるサイズの半導体パッケージにも対応できるという。2026年から量産を始める。

次世代半導体パッケージ向け:

日本電気硝子は、次世代半導体パッケージに向けて、外形寸法が515×510mmという大型のガラスセラミックスコア基板「GCコア」を開発した。

課題は何か:

imecは、業界で関心が高まっている2.5D(次元)/3Dインテグレーション技術の研究開発を加速している。EE Times Europeが、imecのシニアフェローに開発の進捗を聞いた。

3次元実装技術の普及を後押し:

岡本工作機械製作所は、Si(シリコン)ウエハーの裏面からSi貫通電極を露出させることができる「Si貫通電極ウエハー全自動研削装置」を開発した。同装置を用いると、Si貫通電極の形成プロセスを効率化でき、3次元実装した半導体デバイスのコスト低減や歩留まりを向上させることが可能となる。

市場/設備投資

企業価値は「まだ割安」も:

レゾナックは2026年2月13日、2025年12月期通期の決算を発表した。半導体・電子材料領域は大幅に増収し営業利益も四半期単位、年単位ともに過去最高益を達成した一方、ほか領域の減収により全体の売上高は1兆3471億円で前年度比3.2%減、営業利益は半導体・電子材料領域のけん引により1091億円で同18.4%増になった。

6期連続で最高益更新:

ディスコは2026年1月21日、2025年度(2025年4月〜2026年3月)通期の連結売上高が4190億円となり、初めて4000億円を超える見込みだと発表した。純利益も1264億円と6期連続で最高益を更新すると予想している。GPUや広帯域メモリ(HBM)など、生成AI関連の先端半導体需要がけん引する。

田中貴金属やIndiumなど:

半導体において最大の新興市場ともいえるインド。材料メーカーも新たなビジネスチャンスを求めて攻勢をかける準備を整えている。

アポロ、ワコー、浜松、ラピス:

ロームは、滋賀工場および、ローム・アポロ、ローム・ワコー、ローム浜松、ラピスセミコンダクタの国内製造関連4社を、前工程と後工程の製造会社2社に再編すると決定した。

大山聡の業界スコープ(92):

6年ぶりに中国を訪れ、半導体装置展示会「CSEAC」を視察してきた。今回はその模様をレポートする。

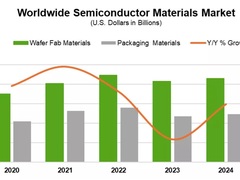

SEMIが発表:

SEMIが発表した半導体材料市場統計レポートによると、2024年の世界半導体材料市場は前年比3.8%増の675億米ドルだった。高性能コンピューティング(HPC)や高帯域幅メモリ(HBM)製造向けの先進材料の需要が増加したことが主な理由だ。

売却額は非公表:

シャープは2025年3月31日、アオイ電子(香川県高松市)との間でシャープ三重事業所第1工場(三重県多気町)の売買契約を締結した。アオイ電子は半導体後工程の生産ライン構築を進め、2027年度の本格稼働を目指す。

2025年度上期に本格稼働:

東芝デバイス&ストレージの姫路工場(兵庫県太子町)で建設していた車載パワー半導体後工程新製造棟が完成した。今後装置の搬入を進め、2025年度上期から本格的な生産を開始する予定だ。

26年初頭に操業開始:

Infineon Technologiesが、タイに最先端の後工程新工場を新設する。製造拠点の最適化とさらなる多極化を目指したもので、2026年初頭に操業開始予定。増加するパワーモジュール需要に対応する。

2026年4月から稼働予定:

Rapidusは、セイコーエプソン千歳事業所(北海道千歳市)内にクリーンルームを構築し、半導体後工程の研究開発拠点「Rapidus Chiplet Solutions(RCS)」を開設すると発表した。2025年4月から製造装置を導入し、2026年4月を目標に研究開発活動を開始する計画だ。

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円