TSMCがドイツに「欧州設計センター」新設へ、25年7〜9月に:技術ロードマップと現状への言及も(2/2 ページ)

TSMCはオランダで開催したイベントにおいて、ドイツ・ミュンヘンに「European Design Center(欧州設計センター)」を設立すると発表した。2025年第3四半期(7〜9月)に開設し、欧州の顧客企業をサポートしていく予定だ。

N3の新規テープアウト数は70超に

また、同社はテープアウトに関して「当社の3nmプロセス技術であるN3は、2025年4月の時点で新規テープアウト数が70を超えていて、量産対応で長年継続可能なノードになる見込みだ」と説明。さらに「N3Pは、N3Eの後継として予定通り2024年第4四半期に量産に入っている(AppleのM4 SoC[System on Chip]は、TSMCのN3Eで製造)。N3のバリエーションとしては、クライアントCPUの性能を向上させるN3Xや、バリュー層製品のコスト効率を高めるN3C、ADAS(先進運転支援システム)や自動運転技術などの車載アプリケーションに向けたN3Aなどが挙げられる」と述べている。

TSMCによると、N3Aは2025年後半の生産開始に向け最終的な欠陥改善を行っていて、AEC-Q100 グレード1認定に向け順調に進展しているという。

TSMCは、自動車市場全体は軟調であるものの、自動運転に向けた先進ロジックであるN4/N3およびN6RFの採用がその成長を「後押し」していると述べた。

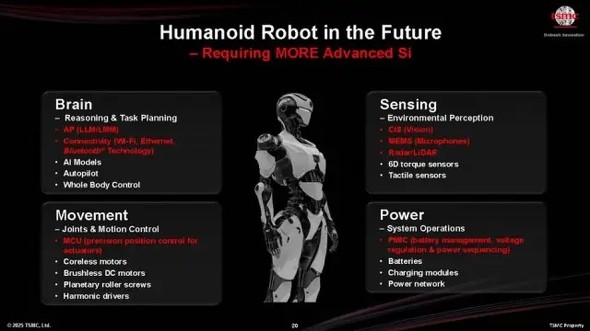

TSMCはまた、ロボット工学および、それがより高度なシリコンへの需要をどのように促進するかという点を注目するテーマの1つとして挙げていた。

N2の先へ……「CFETは有望なスケーリング候補」

これらの先進的なアプリケーションに対応するため、TSMCは2024年12月に米国カリフォルニア州サンフランシスコで開催された「IEDM(International Electron Devices Meeting)2024」でCFET(コンプリメンタリFET)に関する発表内容をフォローアップした。今回のメディアブリーフィングでは「CFETは有望なスケーリング候補で、コンパクトなフォームファクターでの性能向上と消費電力削減に対する需要の高まりに応えるものだ」と述べていた。

また同社は「nチャンネルMOSFET(nFET)とpチャンネルMOSFET(pFET)を垂直に積層することで、CFETは約2倍の密度を達成する」と言及。TSMCはIEDMにおいて、nFETとpFETを同一ウエハー上に集積し、ゲートピッチ48nmで世界最小のモノリシックCFETインバータを実現したと発表していた。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

半導体市場の「勝ち組」と「負け組」

半導体市場の「勝ち組」と「負け組」

大手半導体メーカー各社の2025年1〜3月期の決算が出そろった。各社の業績を比較してみると好不調が明確に分かれている。 TSMCは誰のもの? 米国やAI偏重で懸念される「1本足打法」

TSMCは誰のもの? 米国やAI偏重で懸念される「1本足打法」

TSMCの2025年第1四半期(1〜3月期)は好調で、同四半期としては過去最高を更新した。だがTSMCの売り上げを分析してみると、そこには明らかな「異変」があることが分かる。 ファウンドリー事業への野心燃やすIntel 鍵は「18A」

ファウンドリー事業への野心燃やすIntel 鍵は「18A」

IntelのCEOにLip-Bu Tan氏が就任して初めてとなる四半期決算が行われた。決算は当初の予想を上回る結果だったが、Intelが直面する深刻な状況に変わりはない。改善の鍵の一つとなるのがファウンドリー事業だ。 方便か本気か 分からないTSMCの米国への1000億ドル投資の狙い

方便か本気か 分からないTSMCの米国への1000億ドル投資の狙い

TSMCが米国に1000億米ドルを投じて最先端プロセスの工場を設立すると発表した。しかし筆者としてはその発表がどうもふに落ちない。TSMCの本音はどこにあるのか――。 TSMCが2nm量産へ前進 競合引き離す

TSMCが2nm量産へ前進 競合引き離す

TSMCは、2024年12月に開催された「IEDM 2024」で、2nm世代のプロセス技術「N2」に関する論文を発表した。同社はN2プロセスでの量産を2025年内にも開始する予定だ。 次々世代のトランジスタ技術「コンプリメンタリFET」の構造と種類

次々世代のトランジスタ技術「コンプリメンタリFET」の構造と種類

今回はCFETのトランジスタ構造と、CFETは製造方法の違いによって2種類に分けられることを説明する。