Rapidus、IIM-1を「世界初の前/後工程一貫工場に」:28年度頃の統合目指す(2/2 ページ)

Rapidusは2026年4月11日、製造した2nm先端半導体の解析、評価などを行う「解析センター」および後工程の研究開発拠点「Rapidus Chiplet Solutions(RCS)」を、北海道千歳市に開設した。同日に開所式と記者会見を行い、施設の紹介とともにこれまでの進捗状況、今後の展望を説明した。

26年度の支援額は総額6315億円

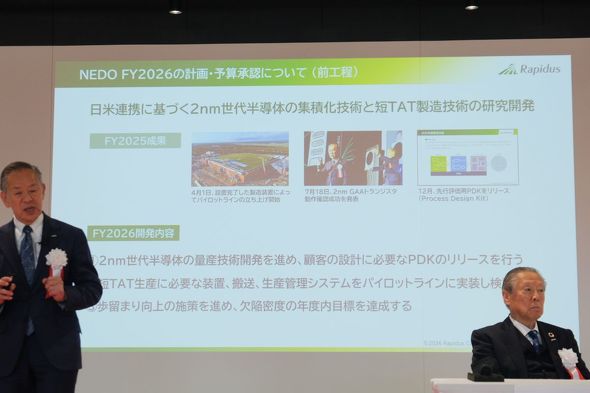

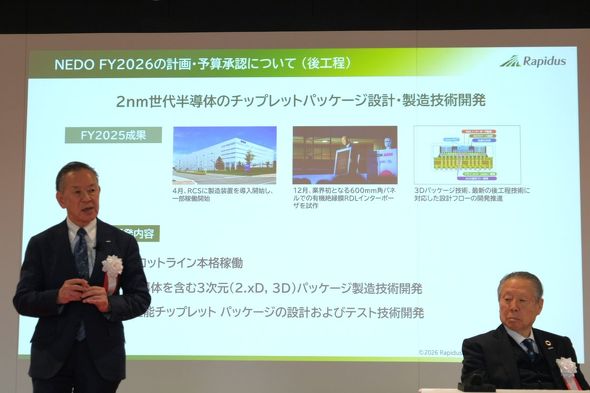

2026年4月11日には、新エネルギー・産業技術総合開発機構(NEDO)から採択を受けている「日米連携に基づく2nm世代半導体の集積化技術と短TAT製造技術の研究開発」および「2nm世代半導体のチップレットパッケージ設計・製造技術開発」で、2026年度の計画、予算が承認されたことも発表している。2026年度の支援上限額は前工程が5141億円で後工程が1174億円、総額6315億円になる。小池氏は2025年度の成果と、それを踏まえた2026年度の目標を説明した。

前工程では2025年4月に2nm先端半導体の生産パイロットラインの立ち上げを開始し、7月に2nm GAA(Gate All Around)トランジスタの動作確認に成功。12月には先行評価用PDK(Process Design Kit)をリリースした。後工程では2025年4月からRCSへの装置導入を開始し、12月には600mm角RDLインターポーザーパネルの試作に成功した。2.xD/3Dパッケージの設計フローも構築している。

2026年度の目標は前工程、後工程ともに大きく3つあるという。「前工程の1つ目は2nm世代の半導体の量産開発技術を進め、顧客が設計に使うPDKをリリースすること。2つ目は短TAT生産に必要な装置、搬送システム、生産管理システムをパイロットラインに実装し、検証すること。3つ目が最も大事な、歩留まり向上の施策を進め、欠陥密度の年度内目標を達成することだ」(小池氏)と語る。

後工程の目標は「1つ目がRCSのパイロットラインを本格稼働すること。2つ目が2nm世代を含む2.xD/3Dパッケージの製造技術を開発すること。3つ目が高効率、高性能チップパッケージの設計および実装技術を開発すること」(小池氏)とする。

「研究開発を充実して、2027年度後半の2nm先端半導体の量産開始や、その先の最先端半導体の量産に着実につなげていきたい」(小池氏)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

キヤノンと日本シノプシスがRapidusに委託へ

キヤノンと日本シノプシスがRapidusに委託へ

キヤノンと日本シノプシスは2026年3月3日、新エネルギー・産業技術総合開発機構(NEDO)の公募事業に採択された次世代半導体の設計技術開発プロジェクトに参画すると発表した。両社はRapidusの2nm GAA(Gate All Around)プロセスを活用する。 Rapidus、総額2676億円を調達 「日本経済に20兆円貢献」期待

Rapidus、総額2676億円を調達 「日本経済に20兆円貢献」期待

Rapidusは2026年2月27日、政府と民間から総額約2676億円の資金調達を実施したと発表した。政府からは約1000億円、民間からはNTTやキヤノン、ソニーグループ、ソフトバンクなど32社が合計約1676億円を出資し、資本金・純資本金の総額は約2749億5000万円になる。 TSMCでも足りないAI需要 Rapidusにチャンスか

TSMCでも足りないAI需要 Rapidusにチャンスか

TSMCは2026年、生産能力拡大に向けて520億〜560億米ドル規模という記録的な設備投資を予定しているが、それでもAIチップ需要への対応には不十分とみられている。アナリストは、TSMCの競合企業が参入機会を得る可能性を指摘している。 Rapidus、千歳で製造した2nm GAAトランジスタの試作品を初展示

Rapidus、千歳で製造した2nm GAAトランジスタの試作品を初展示

Rapidusは「SEMICON Japan 2025」(2025年12月17〜19日)に出展し、北海道千歳市の開発/製造拠点「IIM(イーム)」で製造した2nm GAA(Gate All Around)トランジスタや600mm角 再配線層(RDL)インターポーザーパネルの試作品を展示した。 Rapidus、600mm角インターポーザーパネルを初披露 NVIDIAの受託にも意欲

Rapidus、600mm角インターポーザーパネルを初披露 NVIDIAの受託にも意欲

Rapidus 社長兼CEOの小池淳義氏は「SEMICON Japan 2025」内のセミナープログラムに登壇。同社が掲げるビジネスモデル「RUMS(Rapid and Unified Manufacturing Service)」や前工程/後工程の最新の取り組みを紹介したほか、600mm角の再配線層(RDL)インターポーザーパネルの試作品を披露した。